ORDER NO. VRD9001M103

# Service Manua

Video Cassette Recorder FISHER VHS HQ **FVH-P715**

# **TABLE OF CONTENTS**

| 1. | SPEC  | CIFICATIONS                    |                                         | 2    |

|----|-------|--------------------------------|-----------------------------------------|------|

| 2. | CIRC  | UIT DESCRIPTION                | 3 ~                                     | ~ 80 |

|    | 2-1.  | VIDEO CIRCUIT                  |                                         |      |

|    | 2-2.  | SYSTEM CONTROL CIRCUIT         |                                         | 24   |

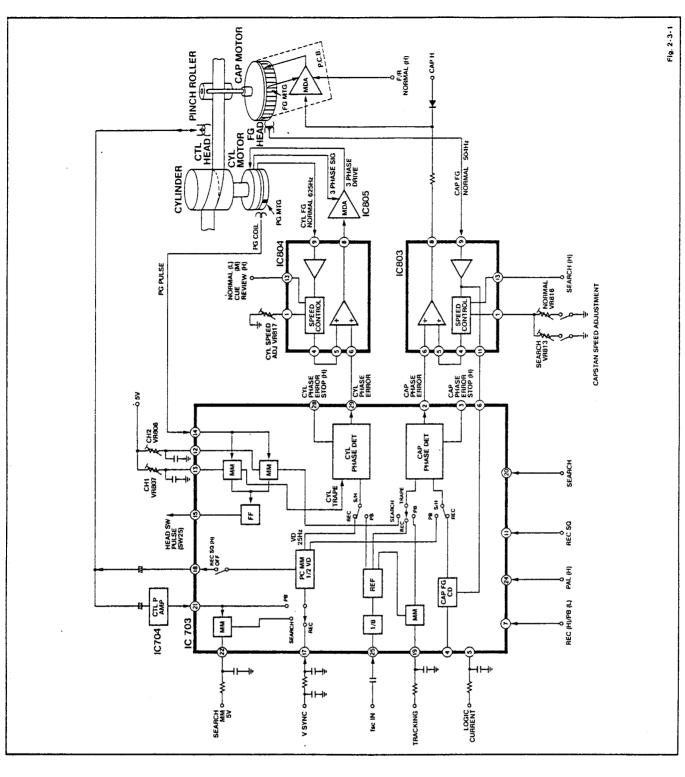

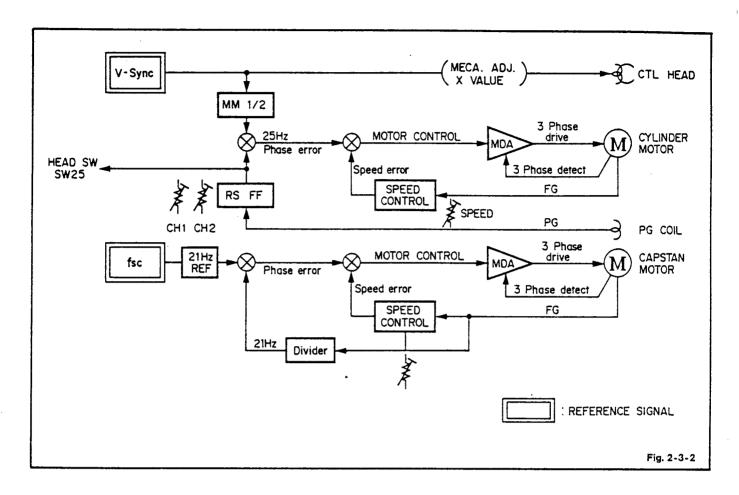

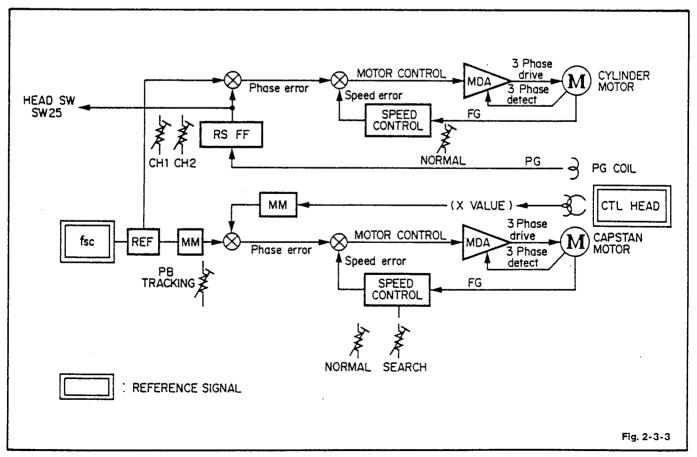

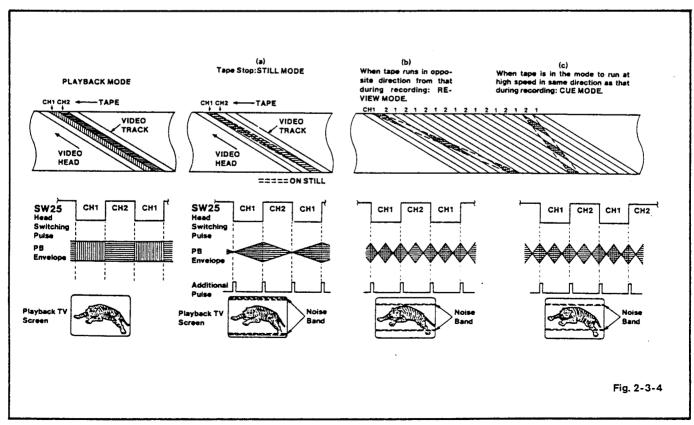

|    | 2-3.  | SERVO CIRCUIT                  |                                         | 48   |

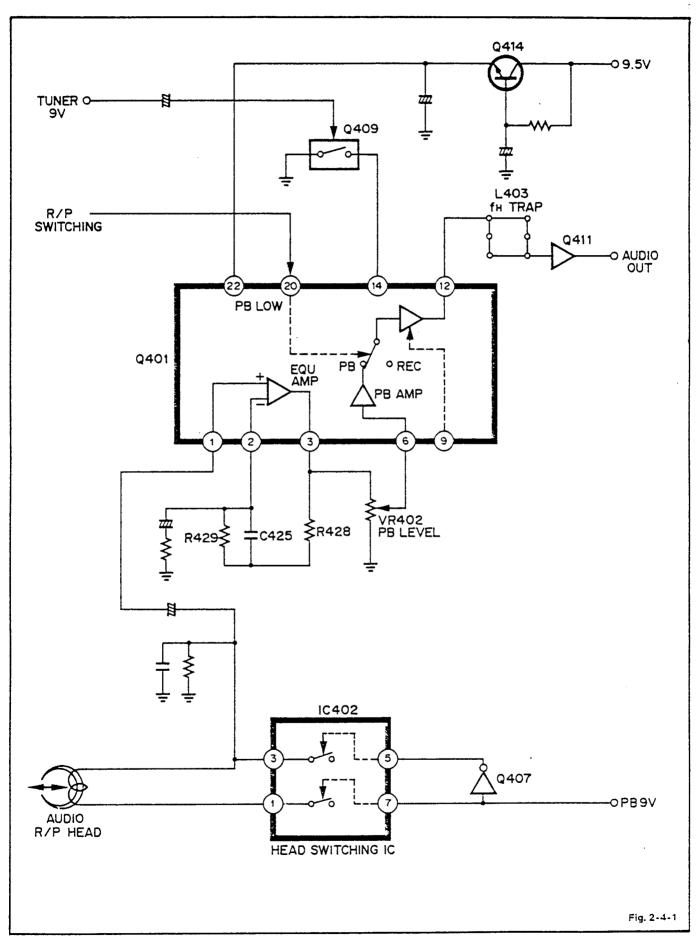

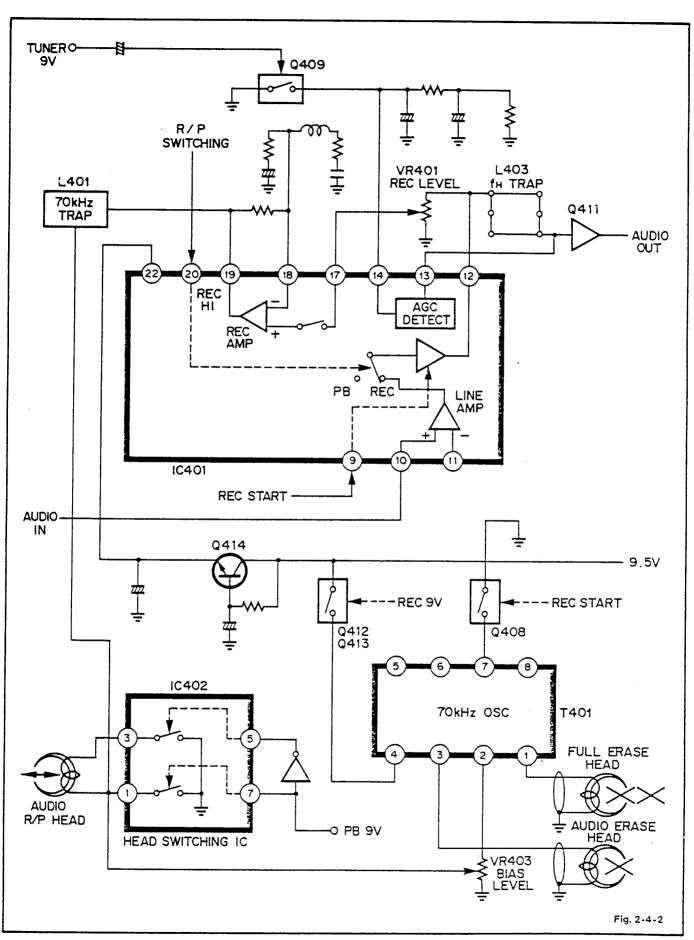

|    | 2-4.  | AUDIO CIRCUIT                  |                                         |      |

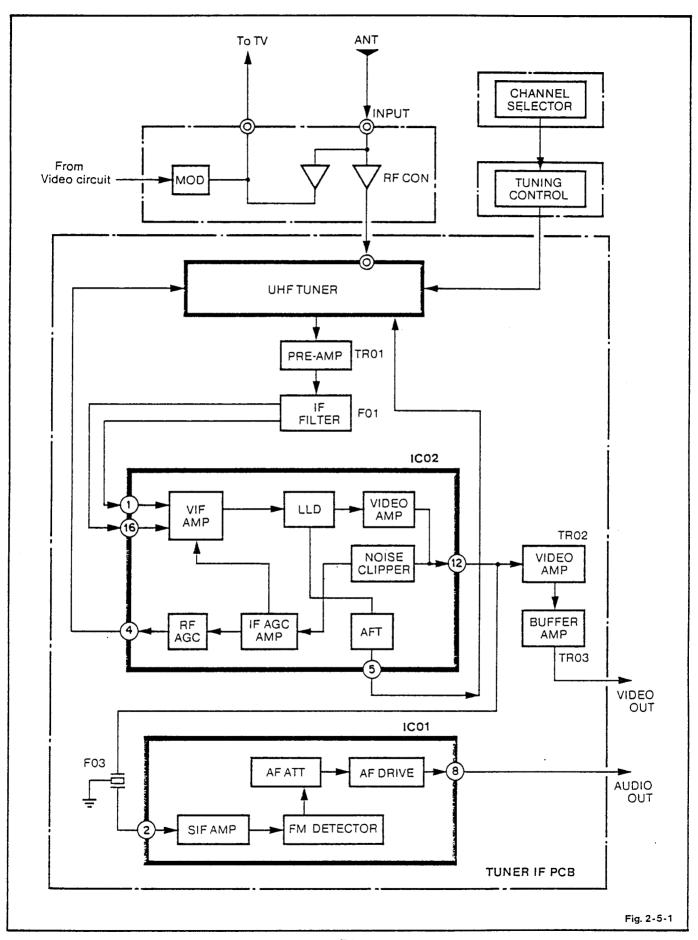

|    | 2-5.  | TUNER CIRCUIT                  |                                         |      |

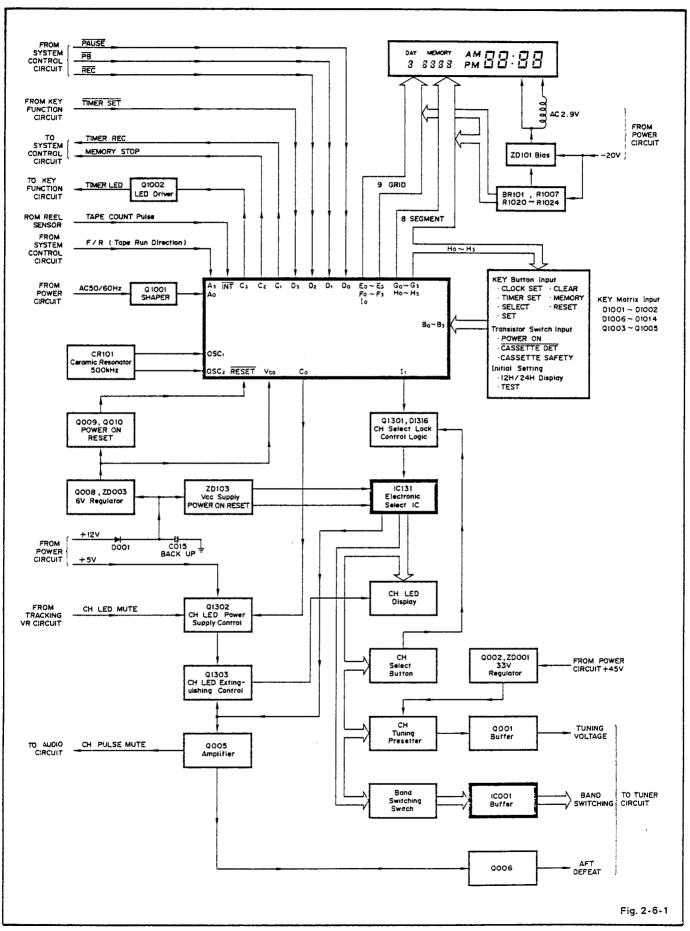

|    | 2-6.  | TIMER CIRCUIT                  |                                         | 72   |

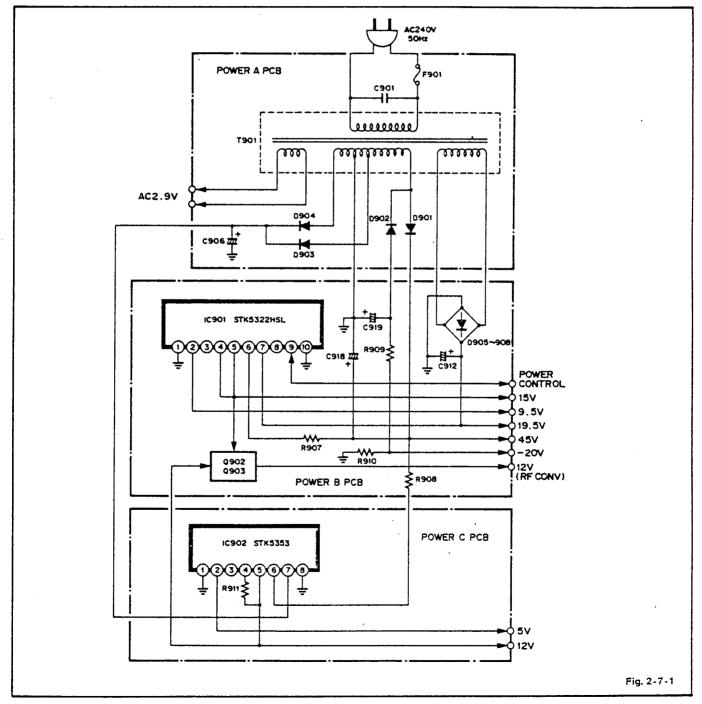

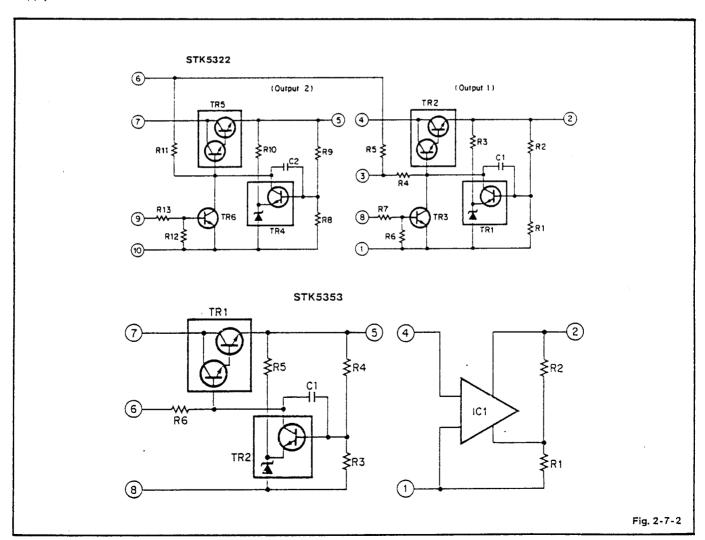

|    | 2-7.  | POWER SUPPLY CIRCUIT           |                                         | 79   |

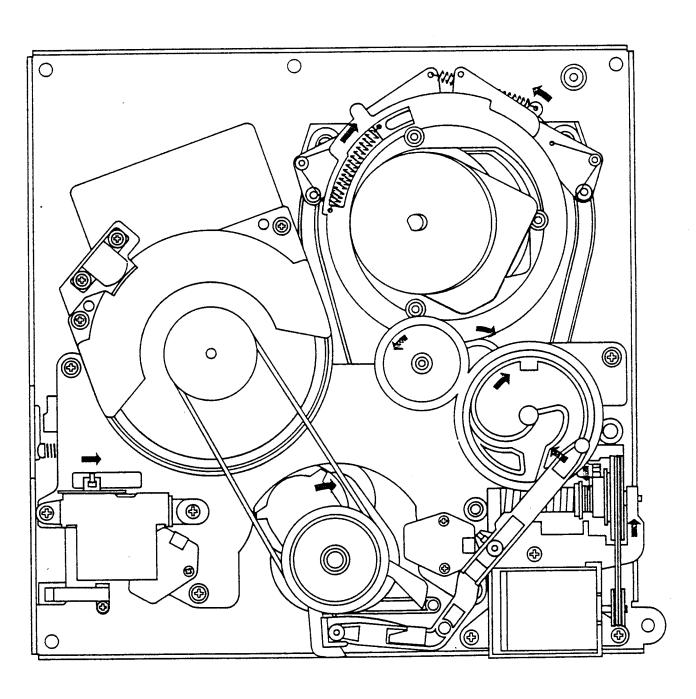

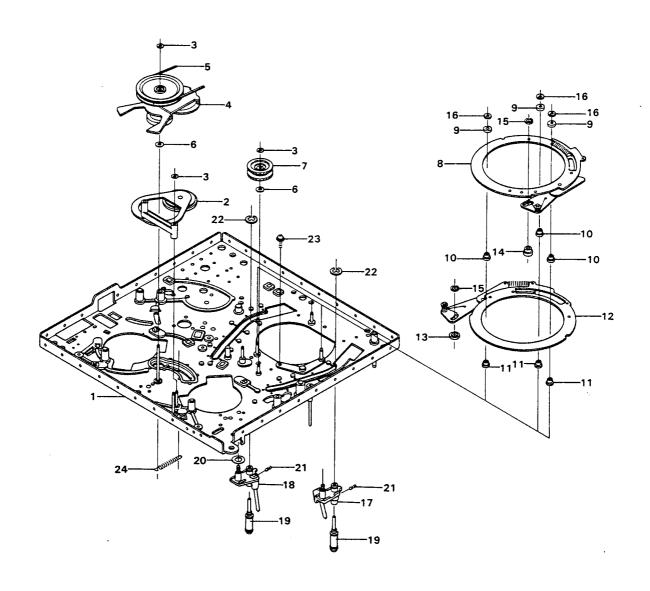

| 3. | MECH  | HANISM DESCRIPTION             | 83~                                     | 109  |

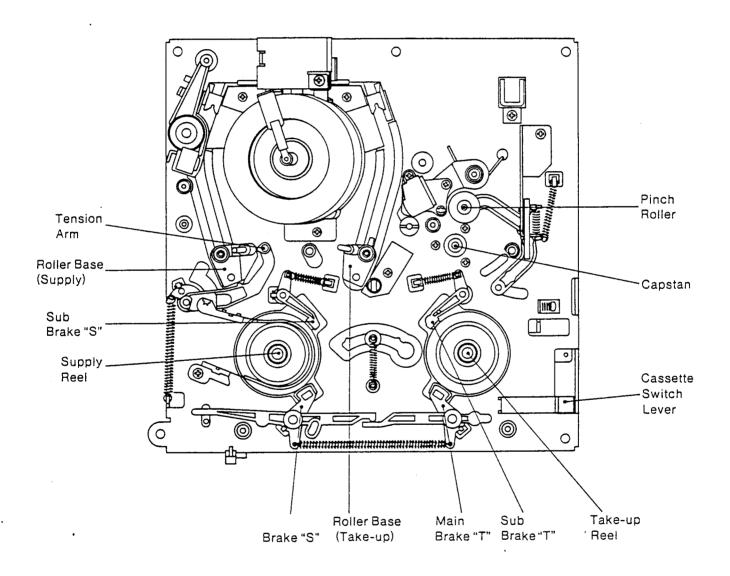

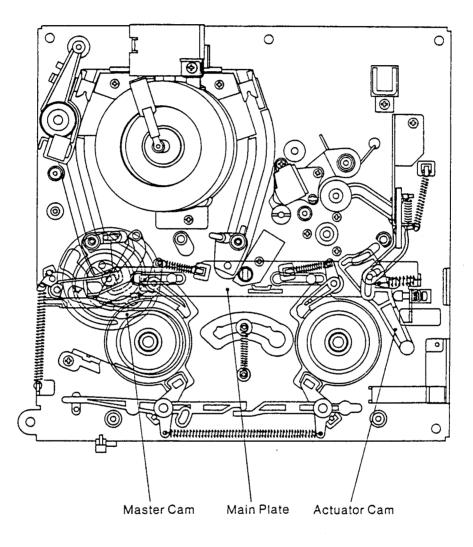

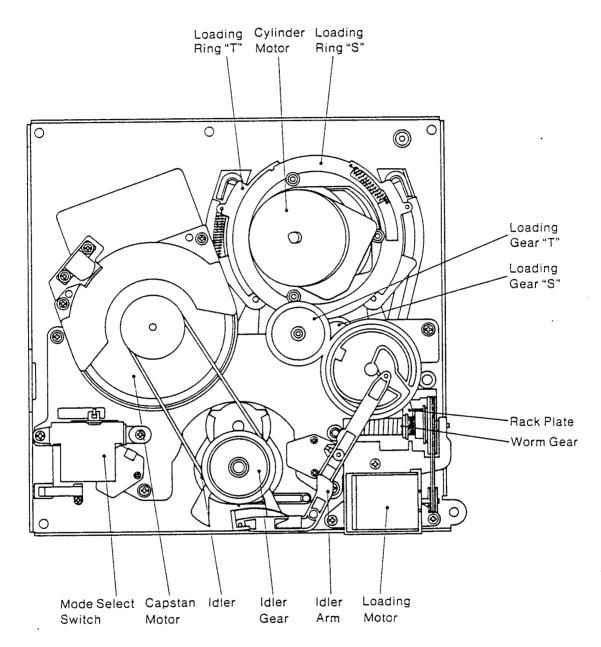

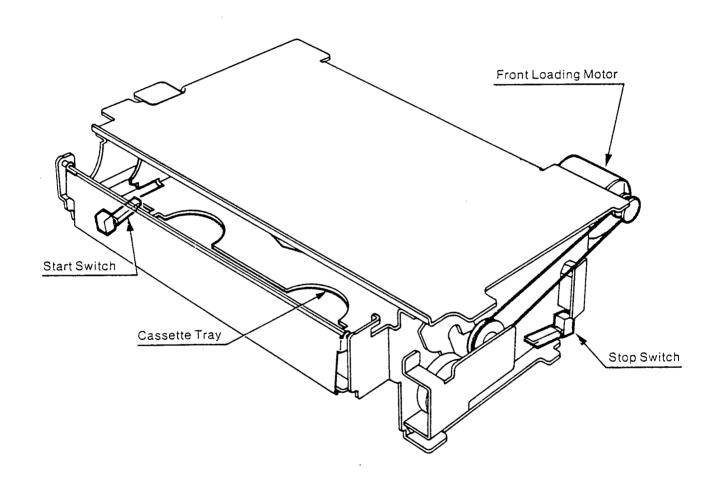

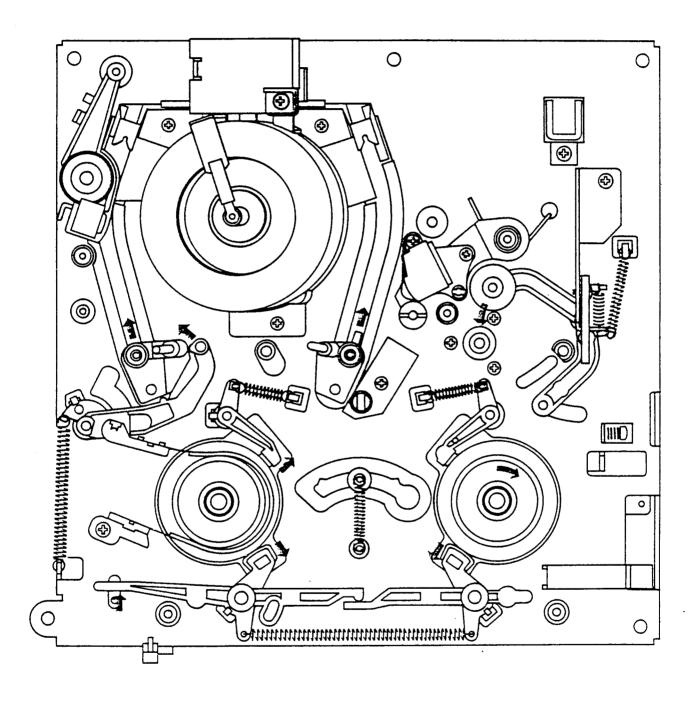

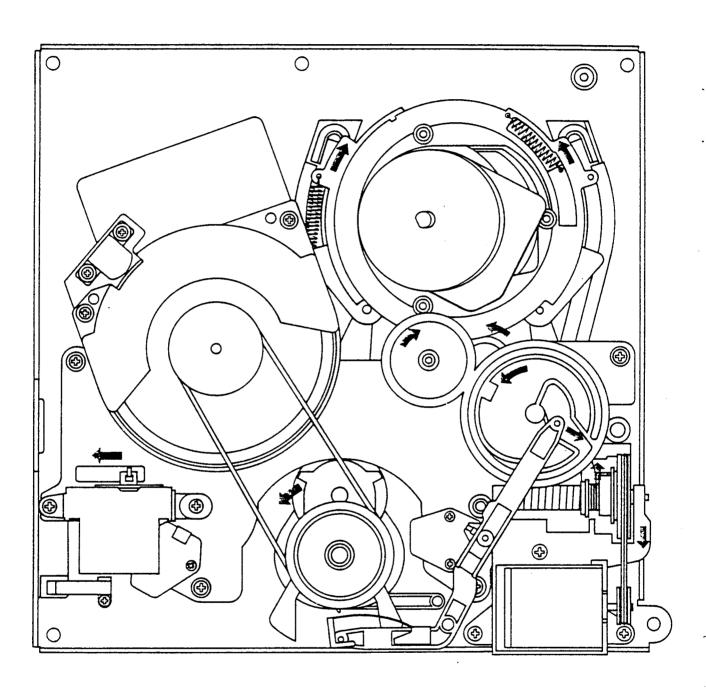

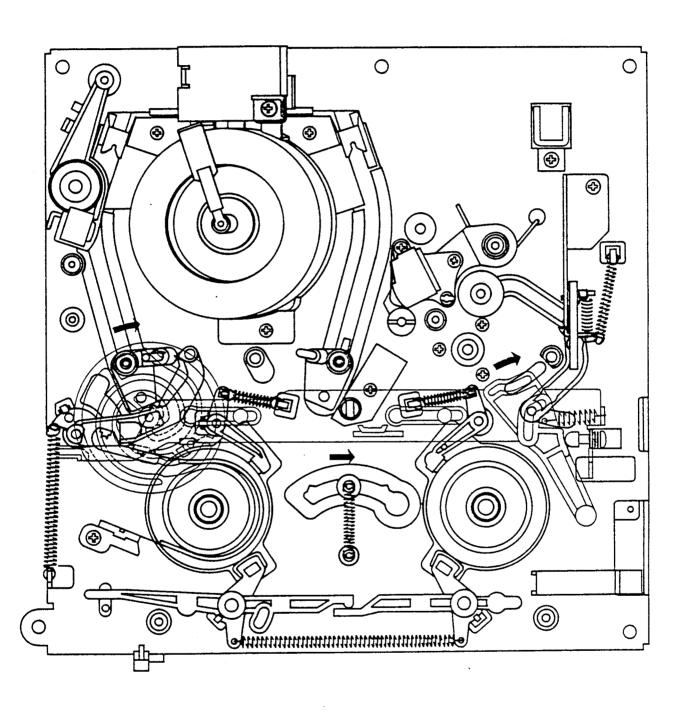

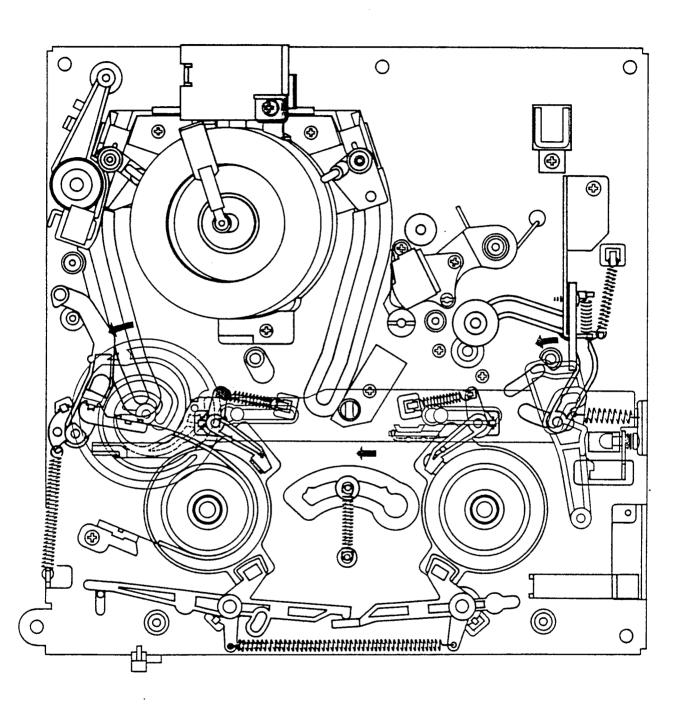

| •  | 3-1.  | MAIN DRIVING PARTS LOCATIONS   |                                         | 83   |

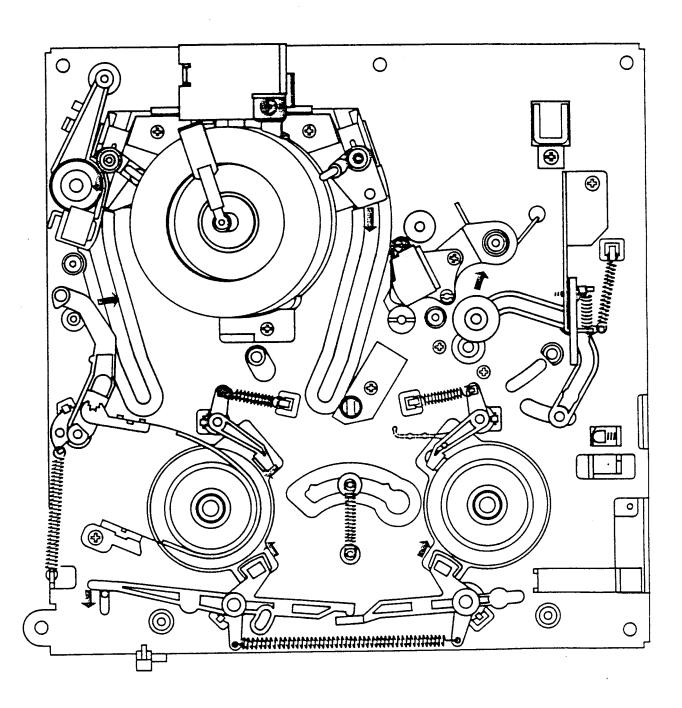

|    | 3-2.  | LOADING MODE OPERATION         |                                         | 87   |

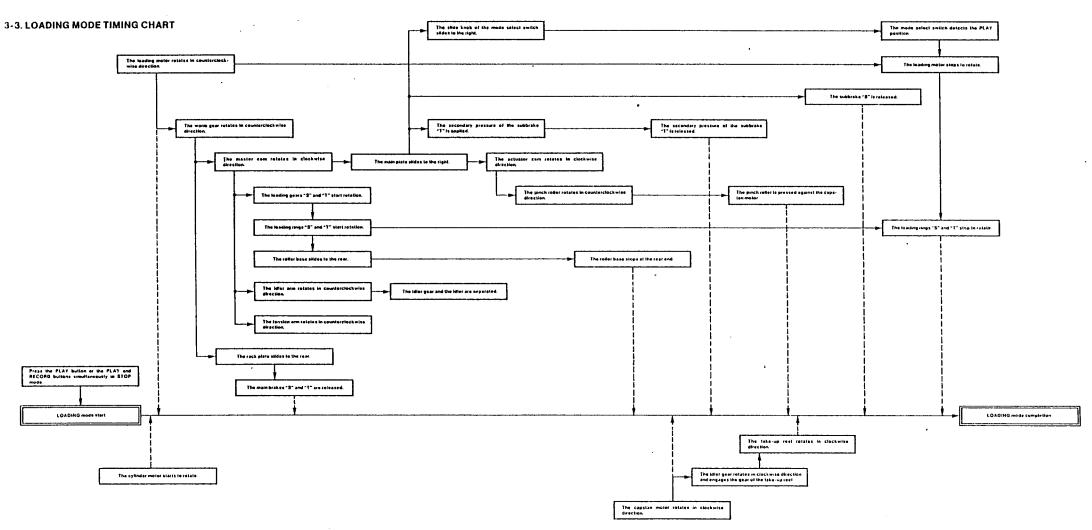

|    | 3-3.  | LOADING MODE TIMING CHART      |                                         | 90   |

|    | 3-4.  | UNLOADING MODE OPERATION       |                                         | 93   |

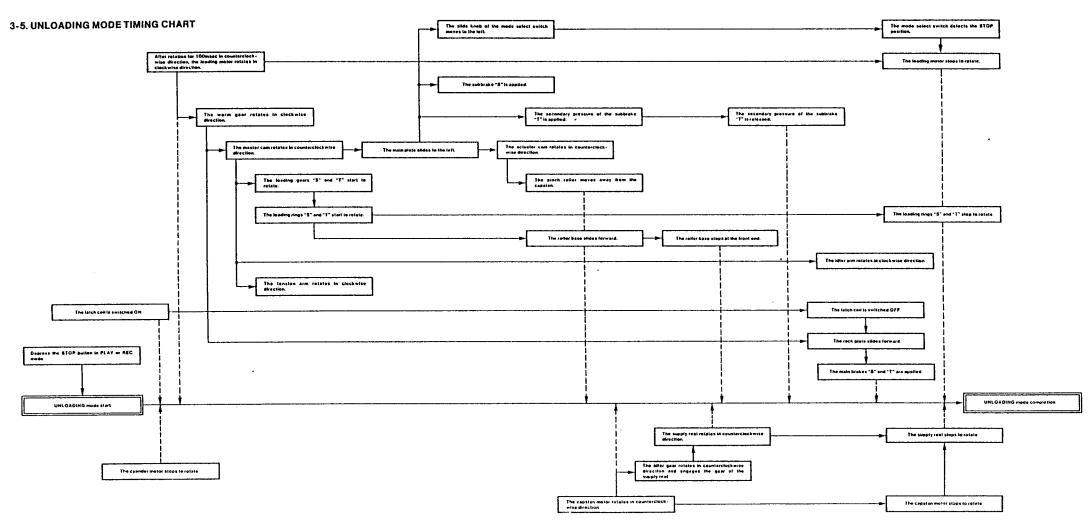

|    | 3-5.  | UNLOADING MODE TIMING CHART    |                                         | 96   |

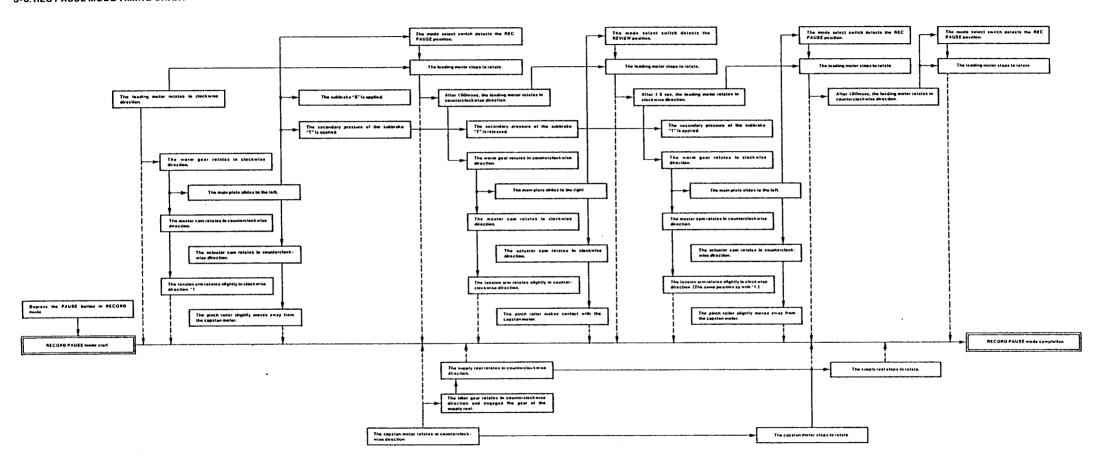

|    | 3-6.  | REC PAUSE MODE TIMING CHART    |                                         | 99   |

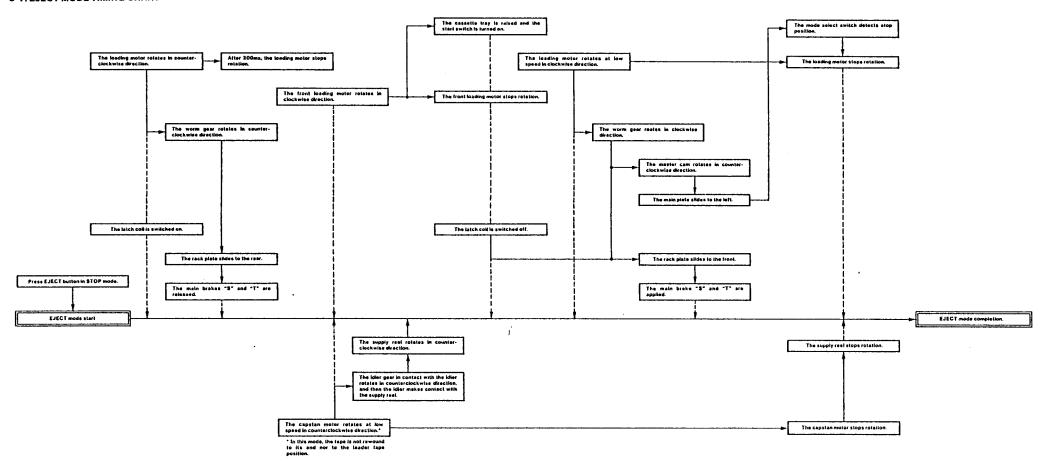

|    | 3-7.  | EJECT MODE TIMING CHART        |                                         | 102  |

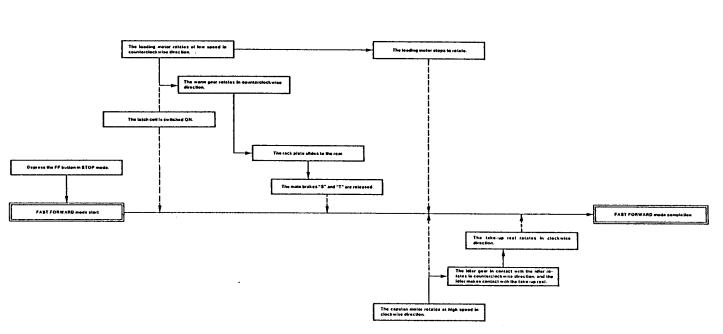

|    | 3-8.  | FAST FORWARD MODE TIMING CHART | • • • • • • • • • • • • • • • • • • • • | 105  |

|    | 3-9.  | REWIND MODE TIMING CHART       |                                         | 107  |

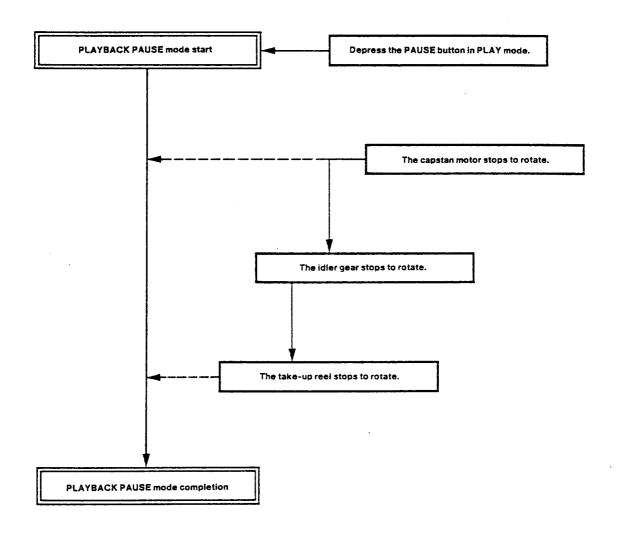

|    | 3-10. | PLAY PAUSE MODE TIMING CHART   | • • • • • • • • • • • • • • • • • • • • | 108  |

|    | 3-11. | CONDITION OF EACH MODE         |                                         |      |

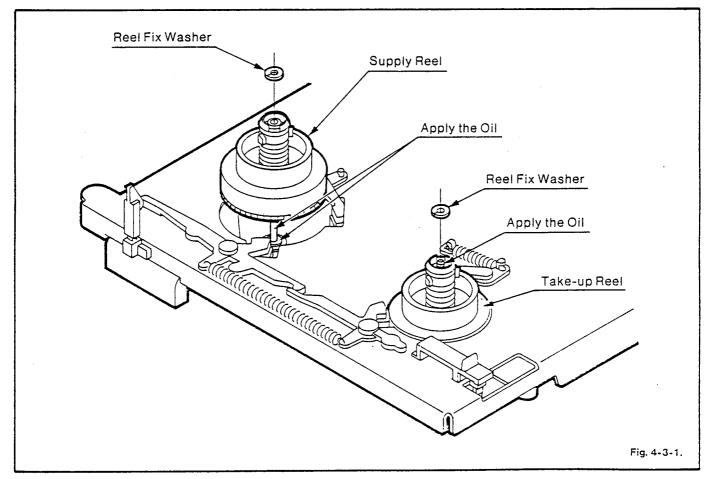

| 4. | MAIN  | TENANCE                        | 110~                                    | 111  |

|    | 4-1.  | MAINTENANCE PARTS AND PERIODS  |                                         | 110  |

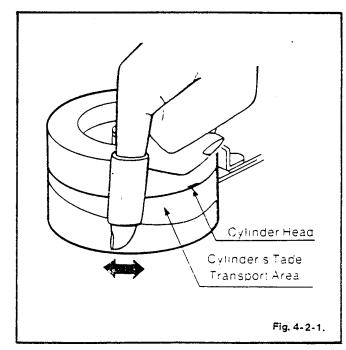

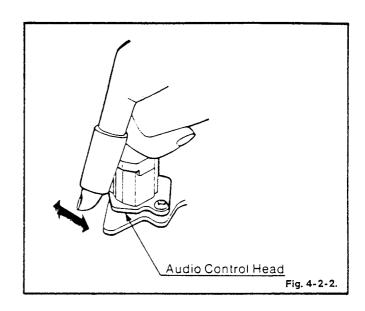

|    | 4-2.  | CLEANING                       | •••••                                   | 110  |

|    | 4-3.  | LUBRICATION                    |                                         | 111  |

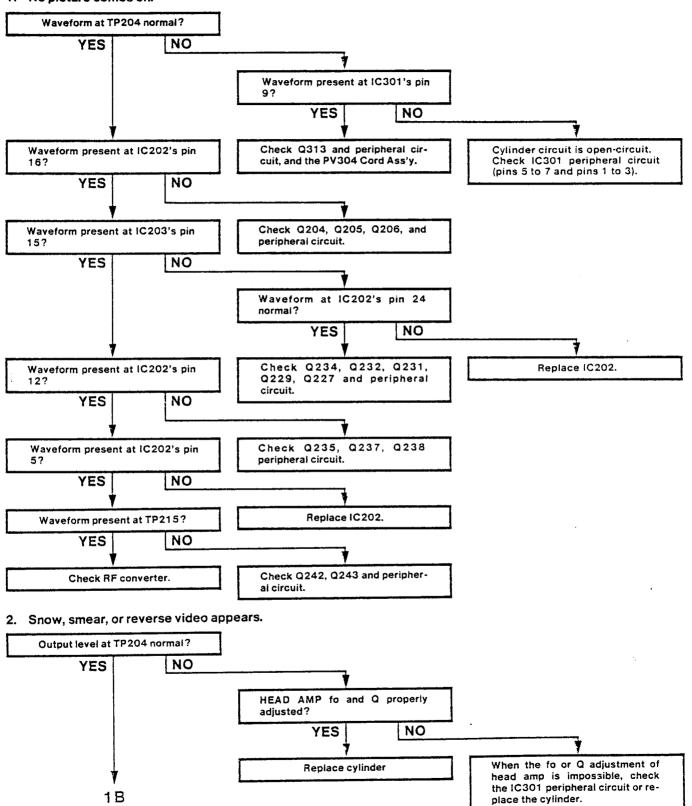

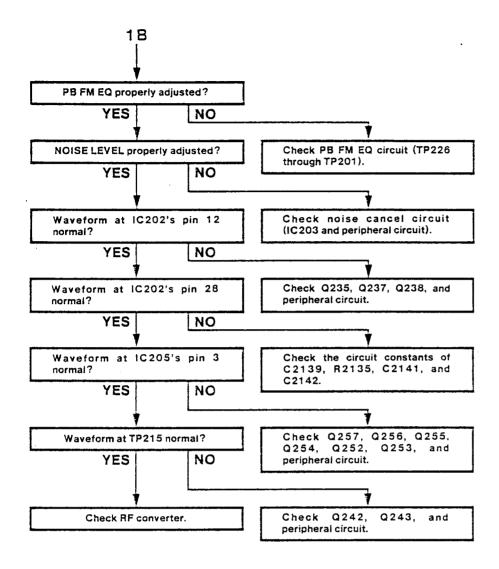

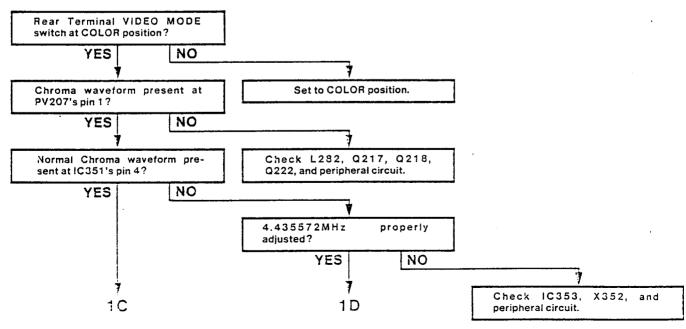

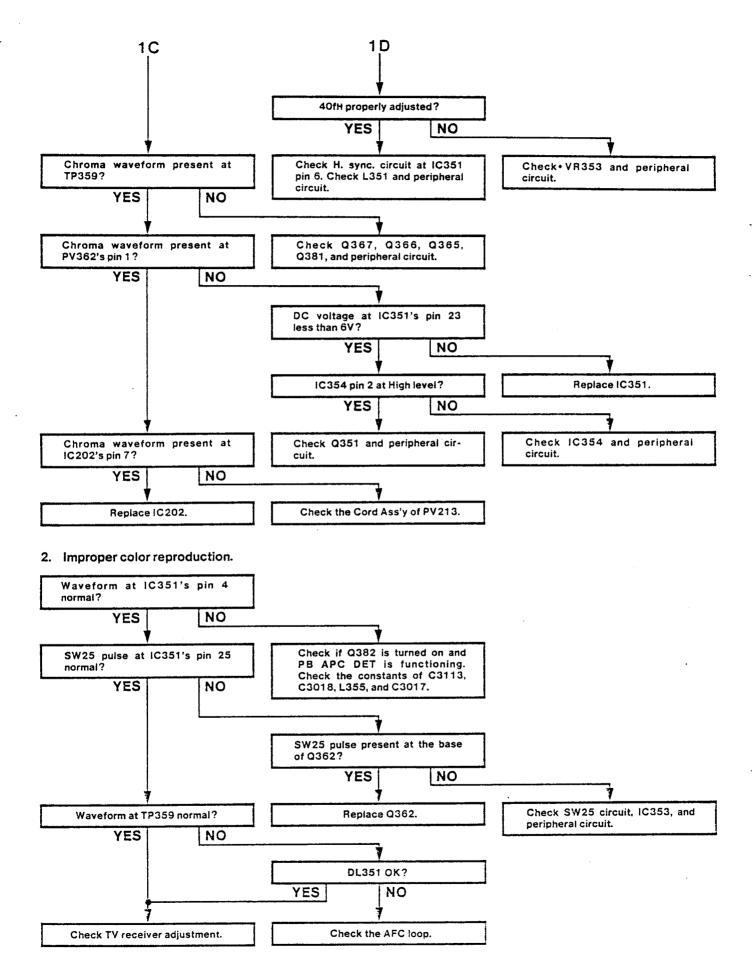

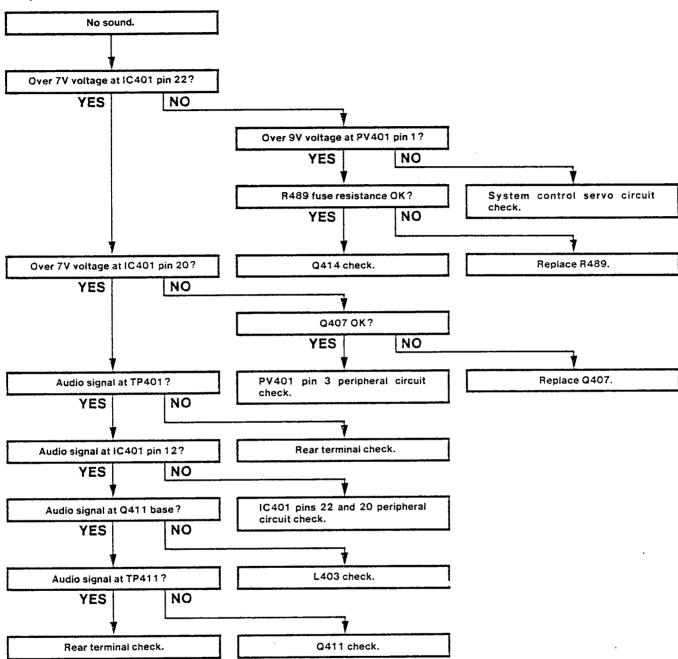

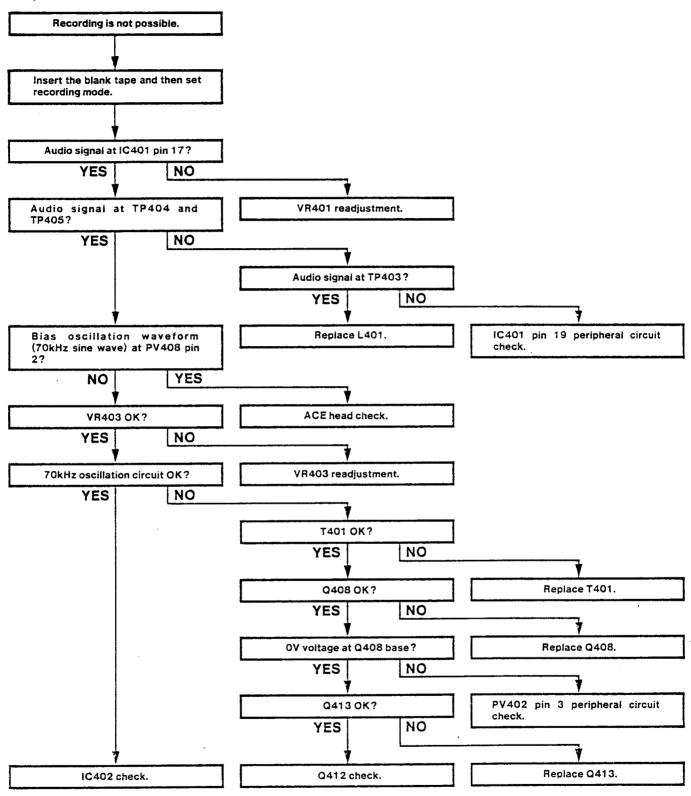

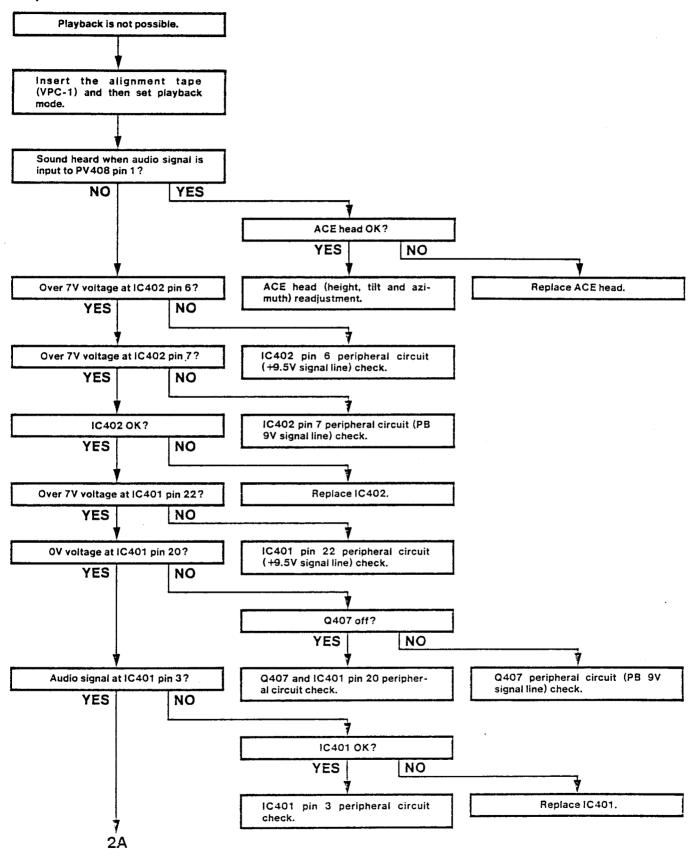

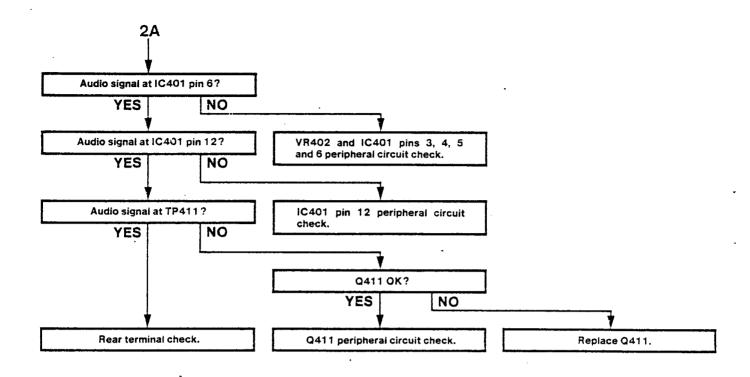

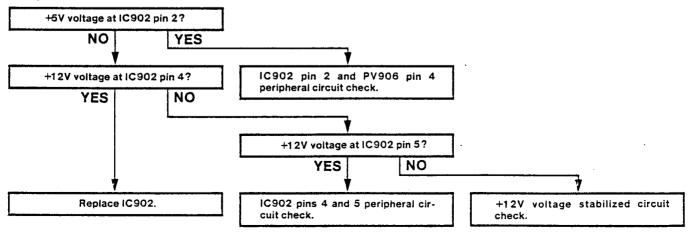

| 5. | TROU  | BLESHOOTING                    | 112~                                    | 158  |

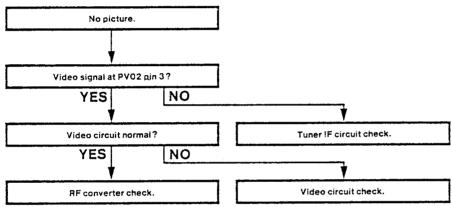

|    | 5-1.  | VIDEO CIRCUIT                  |                                         |      |

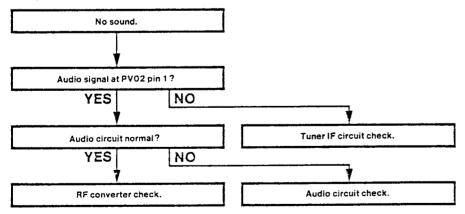

|    | 5-2.  | AUDIO CIRCUIT                  |                                         | 110  |

|    | 5-3.  | SYSTEM CONTROL CIRCUIT         |                                         | 123  |

|    | 5-4.  | SERVO CIRCUIT                  |                                         | 138  |

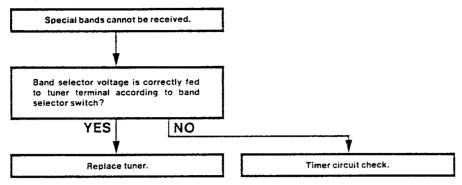

|    | 5-5.  | TUNER CIRCUIT                  |                                         |      |

|    | 5-6.  | TIMER CIRCUIT                  |                                         |      |

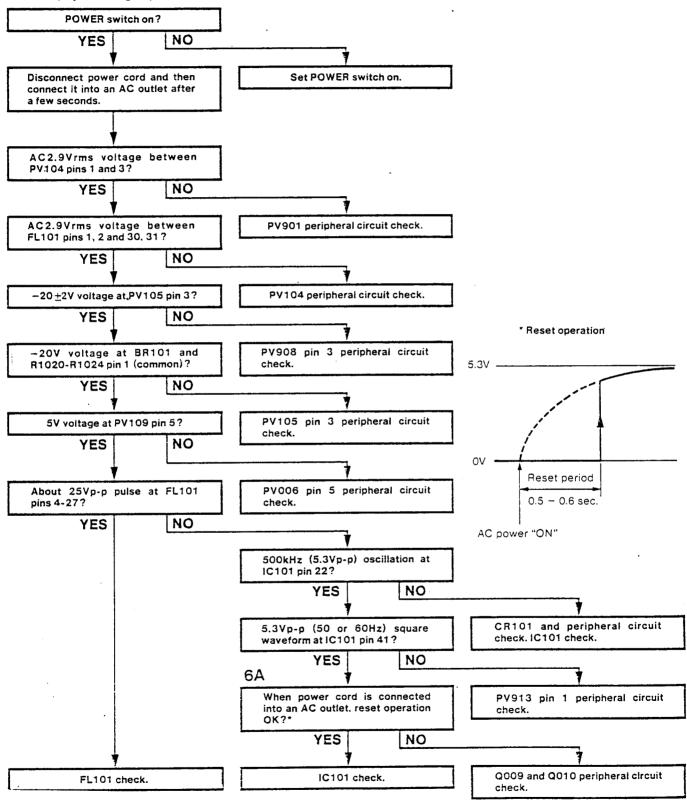

|    | 5-7.  | POWER SUPPLY CIRCUIT           |                                         |      |

# 1. SPECIFICATIONS

# **General Specifications**

Television system

Recording system Format

Tape width

Tape speed

Recording time

Tape loading system

Tuner channel selection system

Tuner channels RF Converter output Time indication

Timer

Tape counter Auto rewind system

**Terminals**

Aerial input RF output

Video input/output Audio input/output Camera remote pause

**Electrical Specifications**

Video output level Video output impedance Audio output level Audio output impedance

Video input level Video input impedance Audio input level

Audio input impedance Video S/N ratio Audio S/N ratio

Audio bandwidth Horizontal Resolution

Other specifications

Power requirement Power consumption

Dimensions

Weight

PAL standard colour (system B & G) & CCIR monochrome signals 625 lines Rotary two-head helical scan system.

VHS PAL standard

12.7mm

22.39mm/sec.

240 minutes with E-240 cassette

Automatic loading

Soft touch, 12 preset channels

UHF: # 21 - # 69

UHF channel 37 (30 - 39 adjustable) AM/PM 12-hour display system

9-days 1 programme

Separate 4-digit electronic display

Activated at end of the tape when FUNCTION

ON switch is pressed

DIN (socket)

DIN (plug)

BNC connects

BNC connector RCA connector

2.5mm jack

1 Vp-p 75 ohm

-6.dB 600 ohm 0.5 - 2.0 Vp-p

75 ohm -20 dB 50 kohm

43 dB 42 dB

50 Hz - 10 kHz Colour 240 lines

nt 240V, 50 Hz

36 Watts

440 mm(W) x 117 mm(H) x 365 mm(D)

10 kg (Approximate)

Because its products are subject to continuous improvement, Fisher Corporation reserves the right to modify product designs and specifications without notice and without incurring any obligation.

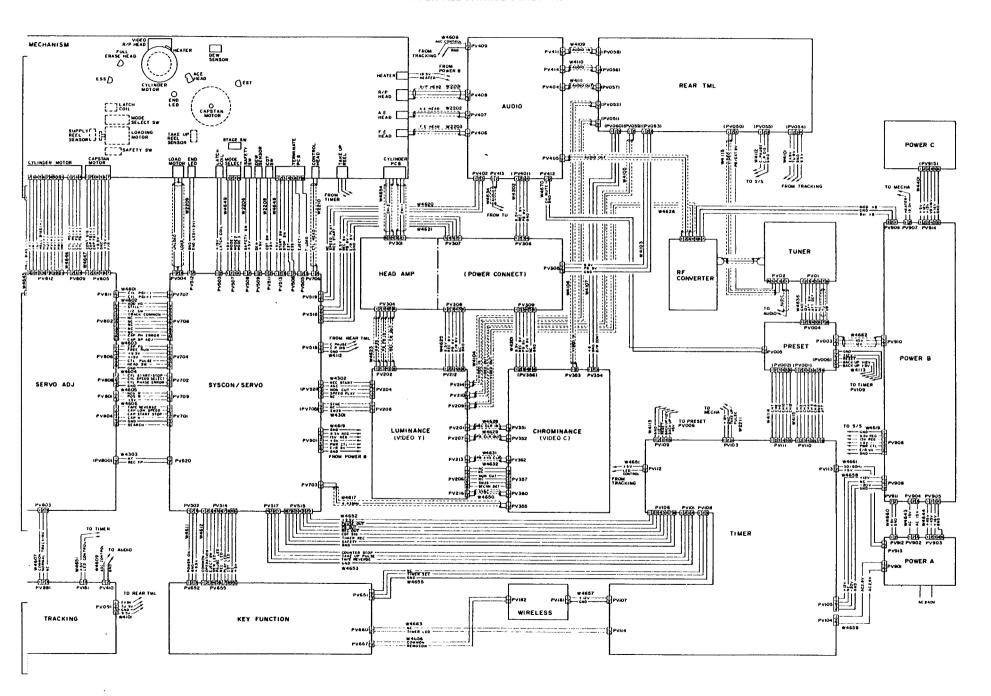

# 2. CIRCUIT DESCRIPTION

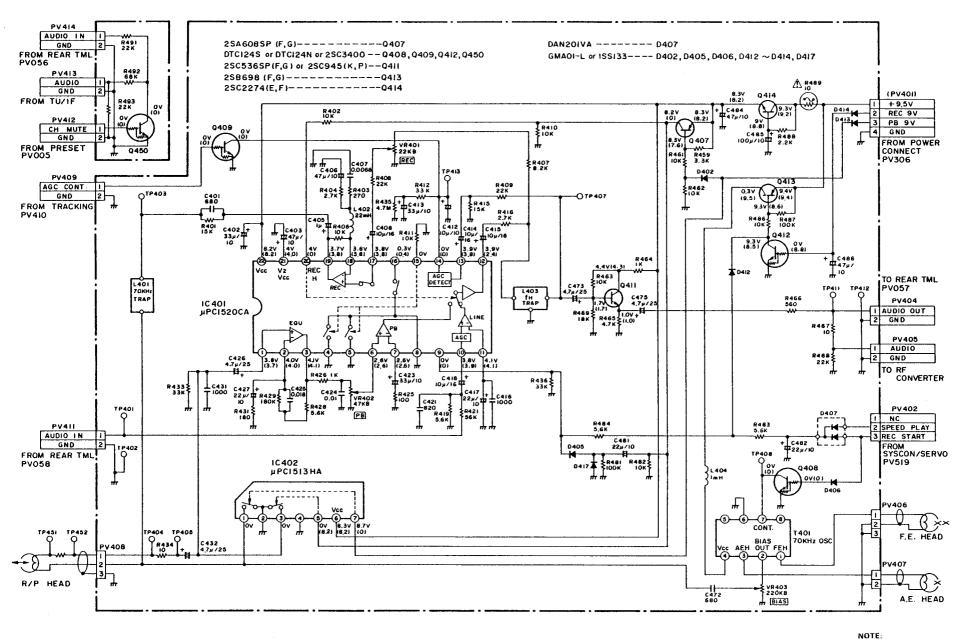

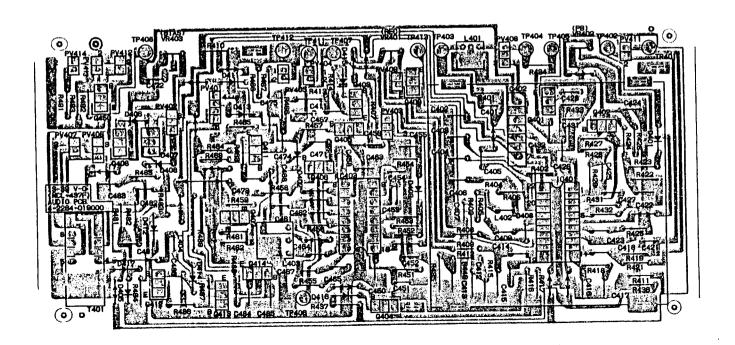

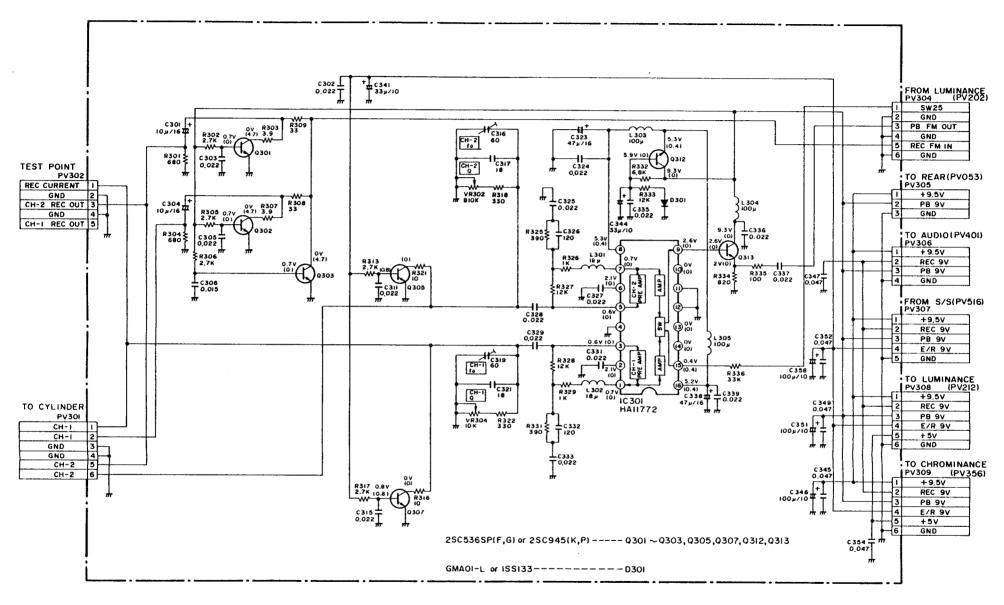

# 2-1. VIDEO CIRCUIT

# 2-1-1. **GENERAL**

The VHS system achieves very low tape consumption and uses low cost video cassette tape. Recording time in the standard play mode has become 4 hours.

Increased recording time results from the narrow gap video heads, high sensitivity video tape and the slant azimuth recording head configuration which eliminates the need for a guard band between recorded tracks. In addition, the VHS format takes into consideration special operating modes such as still picture, slow motion and speed playback.

Adoption of the VHS format presented several technical challenges. Foremost among these were obtaining high picture quality and high resolution despite the slow (4.9 meters per second) relative speed between the tape and video

heads, improving signal to noise ratio (S/N), and preventing black to white reversal phenomena due to the short recording wavelength of  $1.0\mu m$ . Also the  $\pm 6^{\circ}$  azimuth angle of the video heads alone is not sufficient to eliminate crosstalk from the down converted color signal.

Steps for solving these difficulties included adoption of a nonlinear emphasis circuit and selecting the emphasis amount for optimum S/N. The reversal problem was overcome by using a noise canceller circuit, while a phase shift system has been designed for eliminating color crosstalk.

The following discussion covers several main points of the VHS format.

# 2-1-2. MAGNETIC TAPE PATTERN

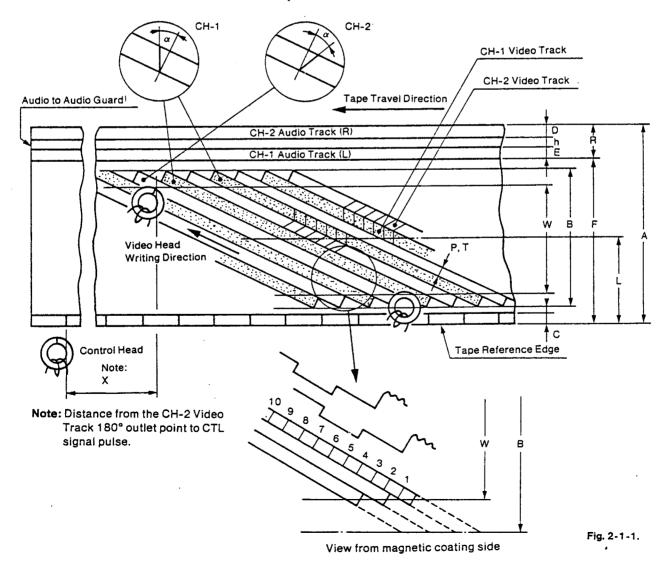

## 1. STANDARD

In the VHS format, two rotating video heads at  $\pm 6^{\circ}$  azimuth angle are used for recording without a guard band.

Fig. 2-1-1 indicates the recording pattern, while the pertinent values are listed in Table 2-1-1.

|     |              | Items                               | Standard | Remarks     |                                            |

|-----|--------------|-------------------------------------|----------|-------------|--------------------------------------------|

| 1.  | (A)          | Tape Width                          | mm       | 12.65 ±0.01 |                                            |

| 2.  | (Vt)         | Tape Speed                          | mm/sec   | 23.39 ±0.5% |                                            |

| 3.  | $(\phi)$     | Drum Diameter                       | mm       | 62 ±0.01    | (Upper Drum)                               |

| 4.  | (Vh)         | Writing Speed                       | m/sec    | 4.85        |                                            |

| 5.  | (P)          | Video Track Pitch                   | mm       | 0.049       |                                            |

| 6.  | (B)          | Video Width                         | mm       | 10.60       |                                            |

| 7.  | (W)          | Video Effective Width               | mm       | 10.07       |                                            |

| 8.  | (L)          | Video Track Center                  | mm       | 6.2         | Measured from reference edge               |

| 9.  | (V)          | Video Track Width                   | mm       | 0.049       |                                            |

| 10. | (C)          | Control Track Width                 | mm       | 0.75        |                                            |

| 11. | (R)          | Audio Track Width                   | mm       | 1.0         | Single track                               |

| 12. | (D)          | Audio Track Width                   | mm       | 0.35        | CH-2 (R)                                   |

| 13. | (E)          | Audio Track Width                   | mm       | 0.35        | CH-1 (L)                                   |

| 14. | (F)          | Audio Track Reference Line          | mm       | 11.65       | Measured from reference edge               |

| 15. | (h)          | Audio to Audio Guard Width          | mm       | 0.3         |                                            |

| 16. | $(\theta 0)$ | Video Track Angle                   |          | 5°56'7.4"   | (Stopped)                                  |

| 17. | $(\theta)$   | Video Track Angle                   |          | 5°57'50.3"  | (Running)                                  |

| 18. | $(\alpha)$   | Video Head Gap Azimuth Angle        |          | 6° ±10'     |                                            |

| 19. | (X)          | Positions of Audio and Control head | mm       | 79.244      |                                            |

| 20. | ( )          | Positions of Front Edge of V-SYNC   |          | 5 ~ 8H      | Inside the W bottom edge                   |

| 21. | ( )          | Tape Back-Tension                   |          | 30 ~ 45g    | At tape beginning and at the drum entrance |

Table 2-1-1 Magnetic tape pattern

**Note:** Tests and measurements shall be made under the following conditions. Temperature:  $20^{\circ}\text{C} \pm 2^{\circ}\text{C}$ , Relative humidity:  $65\% \pm 5\%$

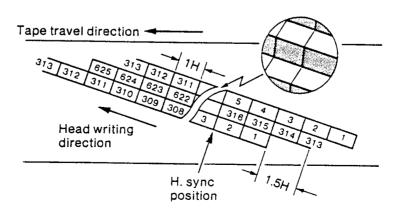

# 2. HORIZONTAL CORRELATION

The azimuth head configuration removes crosstalk from most of the high frequency portion of the FM luminance signal, however, it is not able to fully eliminate crosstalk from the low frequency component of the lower sideband portion. This residual crosstalk is reduced by employing line correlation for the tape pattern.

Line correlation (or "H correlation") consists of arranging the horizontal sync signal positions of adjacent recorded tracks. Since this makes the frequencies of the main signal and crosstalk signal very close, the demodulated crosstalk amount becomes extremely low with respect to the main signal. The type of H correlation used in the VHS format is shown in Fig. 2-1-2.

In order to provide H correlation in the tape pattern, tape speed, head drum diameter and other factors must be decided. The adjacent track correlation in the VHS format is 1.5 H. This 1.5 H difference is important not only for removing low frequency crosstalk from the luminance signal, but also for correcting color signal crosstalk in the SECAM system, for which phase shifting cannot be used.

Fig. 2-1-2.

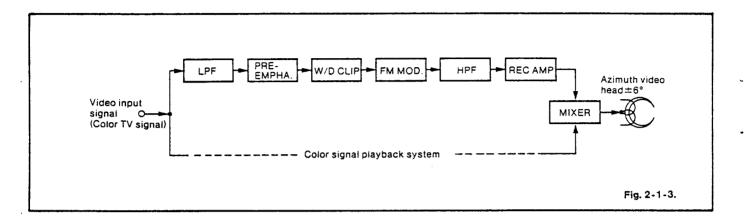

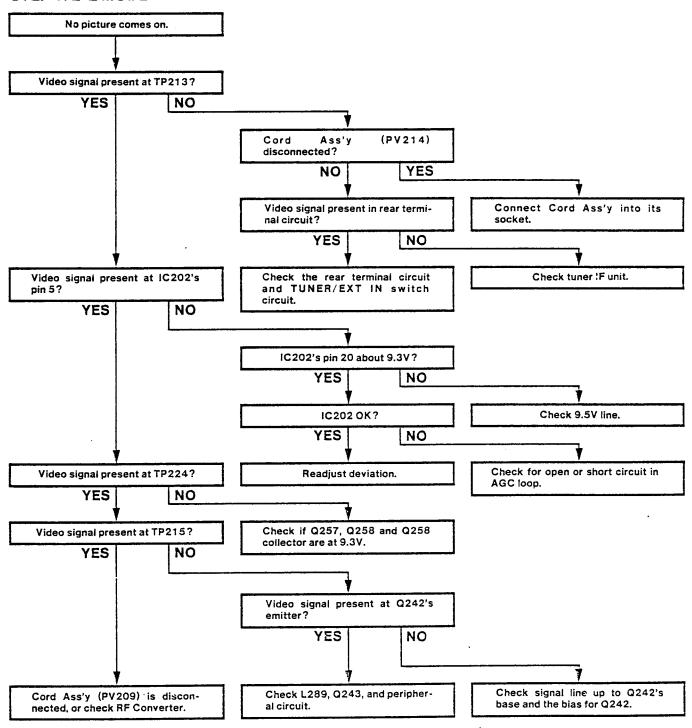

## 2-1-3. LUMINANCE SIGNAL RECORDING SYSTEM

#### 1. GENERAL

Frequency modulation (FM) is used for the luminance signal recording system. A simplified block diagram of the system is shown in Fig. 2-1-3.

A lowpass filter (LPF) removes the color component and passes only the luminance component of the input color TV signal. At the next stage pre-emphasis circuit, the high frequency portion of the luminance signal is enhanced in order to improve S/N during FM recording. Since excess pre-emphasis could lead to black/white reversal due to the shortened recording wavelength, a white/dark clip circuit cuts the overshoot and undershoot components which exceed certain positive and negative levels

The frequency modulator (FM MOD) converts the AM luminance signal to FM, which goes through a highpass filter (HPF) to the recording amplifier. These circuits amplify the signal with the proper frequency characteristic, after which it is mixed with the down converted color signal and supplied to the video heads.

The following describes luminance signal recording and

The following describes luminance signal recording and playback processes (see Figure 2-1-4). The upper section in Fig. 2-1-4 shows luminance signal path in recording mode and lower section shows playback mode.

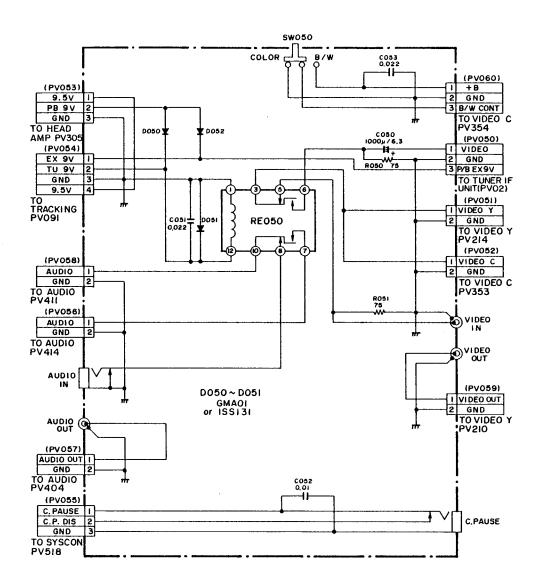

# 2. INPUT SIGNAL SELECTOR CIRCUIT

The video signal is either from the tuner or the rear VIDEO IN jack. One out of these two video signal sources is selected by a relay, which is controlled with the TU-EXT switch.

The selected video signal is supplied to both the luminance and chrominance circuits.

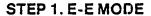

## 3. ELECTRIC ELECTRIC (E-E) CIRCUIT

The E-E circuit allows the user to monitor the signal being recorded at the Line Out jack or to view TV programs using the VTR tuner.

The video signal is supplied to pin 26 of IC202 (luminance circuit), where the signal is amplified through an AGC and E-E amplifiers, then output to pin 5. The signal then goes to a switching transistor (Q258) which selects only the E-E and REC modes, after passign through an emitter follower (Q257). The output of the switching transistor is input to RF converter via an emitter follower (Q242) and RF delay equalizer (L289).

The video signal branched at Q242 is applied to the rear VIDEO OUT jack via an emitter follower (Q244).

The RF converter converts the video signal into a TV signal whose frequency corresponds channels 30 through 39.

The signal being recorded can be monitored at either the RF OUT or Line Out jack using the appropriate monitor.

# 4. AGC CIRCUIT AND 3.5MHz LOW-PASS FILTER (LPF)

The output of the AGC amplifier within IC202 appears at pin 24 of the IC. This output goes to a 3.5MHz LPF (L286) and delay equalizer (L285) via emitter follower (Q234, Q232).

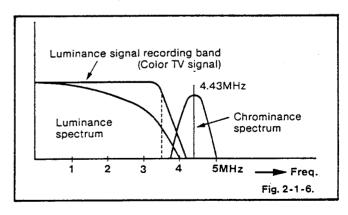

The 3.5MHz LPF separates the video signal into the luminance and chrominance signals. The LPF characteristics are shown in Figure 2-1-6.

The output of the LPF is input to pin 13 of IC202, where the luminance signal is amplified by an internal video amplifier to compensate for the loss caused by the LPF and equalizer. The luminance signal appearing at pin 14 of IC202 branches to a clamp circuit (pin 18 of IC201), sync separation circuit (pin 1 of IC202), and AGC circuit (pin 28 of IC202).

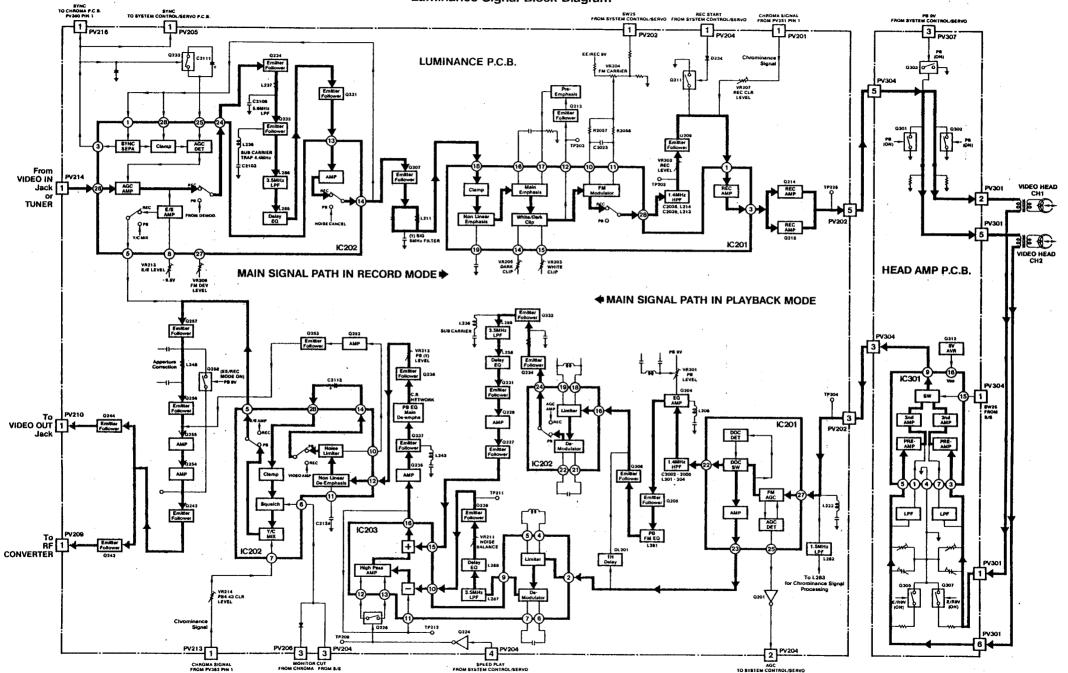

# Luminance Signal Block Diagram

Fig. 2-1-4.

Fig. 2-1-5.

The AGC and sync separation circuits provide the video signal with AGC control. The following describes AGC operations;

The typical ratio of signal levels of the sync signal to the luminance signal (both contained in the video signal) is 3:7. The sync signal contained in the input signal is, however, not constant in its level, and the luminance signal level also varies with the picture brightness.

The sync AGC circuit detects the amplitude of the sync signal level and regulates it to a constant level.

The sync AGC circuit, when the sync signal level is low, increases it, which also increases the luminance signal level. If the luminance signal level is saturated, the picture will loose contrast, with color balance leaned to white, however. To prevent this, the sync AGC functions as a peak AGC when the sync ratio is less than 26.7% (with respect to the luminance signal), so as to regulate the video signal to a constant level.

Figure 2-1-7 shows sync signal ratio versus video signal. If we sassume that the sync signal ratio is 50%, or in other words, the luminance signal is at 30% (gray level) with respect to its peak level, the sync signal component is 0.3 Vp-p and the luminance signal component is 0.3 Vp-p. This provides for an AGC output level of 0.6 Vp-p for the video signal.

The AGC circuit used in this VTR covers a video signal level range of 0.5 to 2 Vp-p to provide a constant video output of 1 Vp-p.

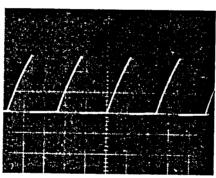

#### 5. CLAMP CIRCUIT

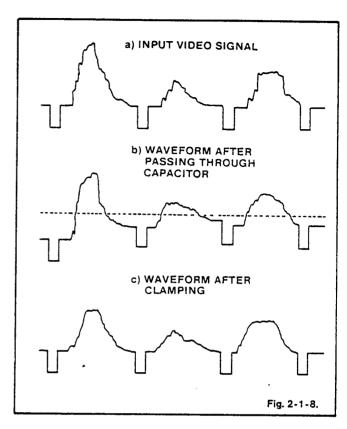

The luminance component of the video signal varies with the brightness (APL) of the picture (Figure 2-1-8(a)). When the signal is passed through capacitor coupling circuit, its DC component is blocked by the capacitor, resulting in irregular tip levels of the sync signal (Figure 2-1-8(b)). The clamp circuit is used to align the lower limit of the modulation frequency to the sync tip level in the following FM modulator.

The clamp circuit is contained in IC201, whose pin 18 presents a clamped waveform (Figure 2-1-8(c)).

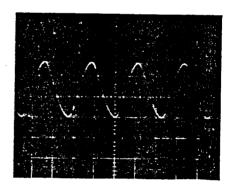

## 6. EMPHASIS CIRCUIT

In FM modulation-demodulation system, demodulation noise linearly increases according to modulation signal level. This results in reduced signal-to-noise ratio in high frequency range.

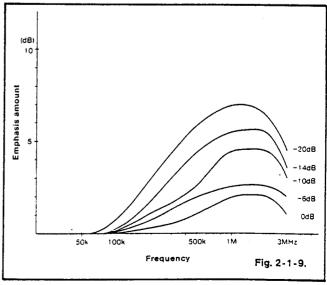

To improve the S/N ratio, the signal level in high frequency range is emphasized beforehand during recording. This method is called pre-emphasis. The pre-emphasis is composed of non-linear emphasis and main emphasis. A low-level luminance signal has a lower S/N ratio than a high-level luminance signal. To compensate for this, the non-linear pre-emphasis technique is used, in which emphasis is increased for low-level input and reduced for high-level input. The emphasis characteristic is controlled by the capacitor connected to pin 19 of IC201.

Figure 2-1-9 shows a non-linear emphasis characteristic.

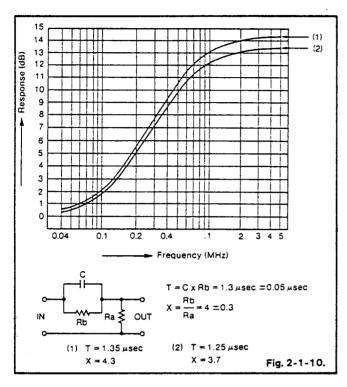

The main emphasis circuit emphasizes the high frequency spectrum independent of the signal level. The luminance signal is fed back from pin 12 of IC201 to pin 17 via Q213 and C.R. circuit which provides the emphasis frequency characteristic. The main-emphasis characteristic is shown in Fig. 2-1-10.

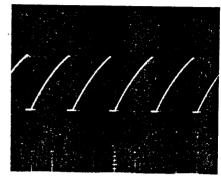

# 7. FM MODULATOR

After going through the pre-emphasis, white clip, and dark clip circuits, the luminance signal is input to an FM modulator, where it is modulated into an FM signal.

The FM modulator uses an astable multivibrator, whose time constant is determined by capacitor C2025 (120 PF) and resistors R2056 (6.8 k $\Omega$ ) and R2057 (6.8 k $\Omega$ ).

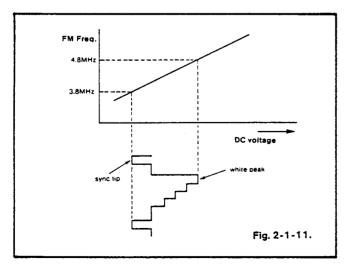

The FM carrier frequency is controlled with VR204 to set the sync tip to 3.8MHz.

The luminance signal level is controlled with VR209 connected to pin 27 of IC202, so that the white peak is at 4.8MHz to achieve the specified frequency deviation.

Figure 2-1-11 shows a relationship of the luminance signal with FM frequency.

## 8. WHITE AND DARK CLIP CIRCUIT

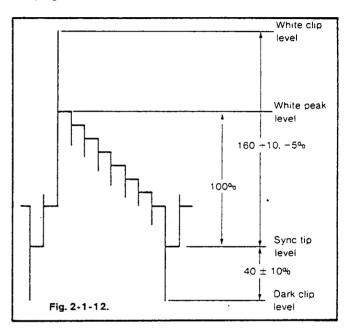

The luminance signal, after passing through the preemphasis circuit, produces sharp overshoot and undershoot at the leading and trailing edges as shown in Figure 2-1-12 because its high frequencies is emphasized. If this signal is directly modulated, the overshoot or undershoot will cause an overmodulation, which will result in a reverse video at the boundary of black and white on the demodulated picture.

On the other hand, a reduced overshoot or undershoot causes reduction of resolution. As a compromise, the VHS standard specifies an overshoot/undershoot clipping level.

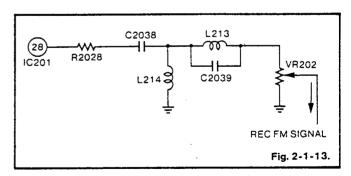

# 9. 1.4MHz HIGH PASS FILTER (HPF)

After FM modulated, the luminance signal output appears at pin 28 of IC201. This output goes to the HPF shown in Figure 2-1-13, where the frequency component below 1.4MHz is attenuated. This prevents beat interference between the low frequency component below 1.4MHz passed through the modulator and the down-converted chrominance signal.

# 10. LUMINANCE/CHROMINANCE MIXER CIRCUIT

After passing through the 1.4MHz HPF, the FM signal is adjusted by VR202 (rec y level adjust.) to the optimum recording current via emitter follower (Q209). The luminance signal is sent to pin 1 of IC201.

In the mean time, the down-converted chrominance signal passed through the 1.5MHz LPF is adjusted by VR207 (rec C level adjust.) and then applied to pin 1 of IC201, where it is mixed with the luminance signal.

#### 11. REC AMPLIFIER CIRCUIT

The signal is amplified by a rec amplifier within IC201 to approximately 20dB, and the output of the amplifier appears at pin 3 of the IC. The output signal is supplied to the head amplifier via an amplifier (Q214, Q215).

# 2-1-4. LUMINANCE SIGNAL PLAYBACK SYSTEM

#### 1. GENERAL

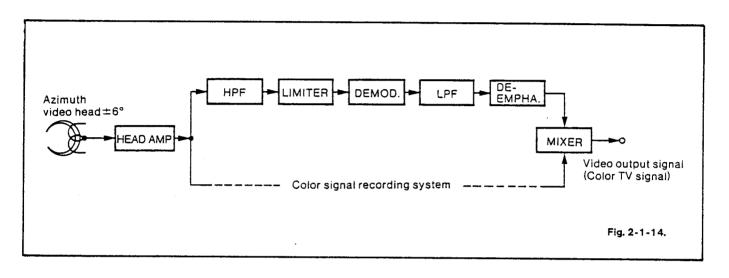

This system functions to return the signals recorded on the tape to a form as close as possible to the video input signals. The simplified block diagram is shown in Fig. 2-1-14.

The low level FM signals played back by the two video heads are combined into a single FM signal by the switching amplifier. After amplification to the required frequency characteristic, a highpass filter attenuates the down converted color signal and passes only the FM luminance signal. This HPF has the same response as that of the recording system.

Variations in the playback FM signal level due to mechanical stretching and contraction of the tape, and irregularities in tape to head contact, are corrected by the limiter circuit. The signal is amplified more than 80dB to permit precise demodulation. A double limiter circuit is employed in order to prevent black/white reversal effects.

In the following stages, the demodulator and lowpass filter return the luminance signal to its AM form. The deemphasis circuit reverses the emphasis applied during recording. From this point, the signal goes to the mixer where it is mixed with the playback color signal to become the video output signal.

The output signal from the head amp is supplied to luminance P.C.B. via PV304 pin 3.

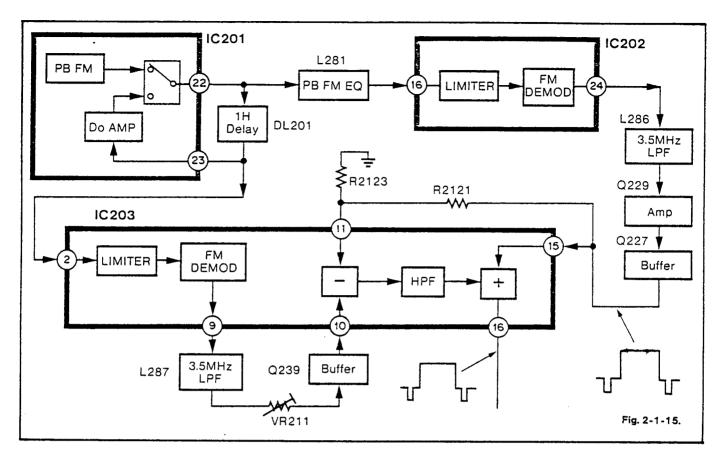

## 2. PLAYBACK FM EQUALIZER

The PB FM signal from head amplifier is supplied to IC201 pin 27 via PV202 pin 3. The unevennes of play-back signal is removed by the AGC circuit inside IC. The AGC output appears at pin 22 via DOC switch circuit, and is input to 1.4MHz HPF where the down-converted chrominance signal is eliminated.

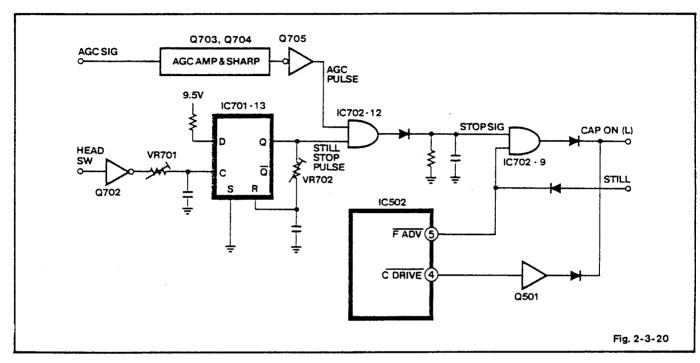

In the meantime, the AGC detector output from IC201 pin 25 is supplied to system control circuit via Q201 and PV204 pin 4. This output is used with the stop pulse signal transmitted from microprocessor inside the system control circuit to stop the capstan motor at the optimum timing to fade out the noise bar in the STILL mode.

The amplified and aligned FM signal then goes to a FM equalizer, where its frequency and phase characteristics are equalized. The equalizer restores a flat frequency characteristic for the playback output of the video head whose high and low frequency characteristics are both attenuated. The equalizer is composed of Q204, Q205, Q206 and L281.

The output of Q206 is input to pin 16 of IC202, where the FM signal is converted into an AM equivalent. The output of Q206 also branches to pin 23 of IC201 via an 1H delay line to serve as a DOC compensation signal. The output of the 1H delay line also goes to pin 2 of IC203, a noise canceller.

## 3. DROP-OUT COMPENSATION CIRCUIT (DOC)

A dropout of magnetic body off the tape surface or dust particle on it causes white horizontal line noise on the playback picture. This is called a dropout. In most cases, the luminance signal is missing or its level is extremely low at dropouts. The DOC circuit serves to making dropout noise inperceptible on the screen.

The DOC utilizes the line correlation principle for TV signal (i.e. the signals on scanning lines which departs 1H from each other on a TV picture are almost identical). The DOC circuit inserts the signal of 1H before into the dropout portion to make it inperceptible on the screen. The signal delayed by 1H is supplied by an 1H delay line (DL201) to pin 23 of IC201.

# 4. H CORRELATION NOISE CANCELLER

The H correlation noise canceller provides noise reduction by utilizing the line correlation principle for TV signals. When the luminance signal on the main signal line and a luminance signal with 1H delay are applied to the inputs of a differential amplifier, the amplifier provides only noise component without line correlation at its output. The noise component is added to the main luminance signal line with the phase in reverse to cancel the noise component.

The block diagram of the noise canceller is shown in Figure 2-1-14.

The main luminance signal is applied to pin 16 of IC202, where it is demodulated via a limiter. The demodulated signal goes to a 3.5MHz LPF (L286) via an emitter follower (Q234, Q232), where the luminance signal includes sync component.

The attenuated luminance signal by LPF is amplified by an amplifier (Q229), then is input to pin 15 of IC203.

The FM signal, after passing through a 1H delay line (DL201), is input to pin 2 of IC203, where it is demodulated via a limiter within the IC.

The demodulated output appears at pin 9 of IC203, and inputs to a 3.5MHz LPF (L287), where unnecessary high-range component is out off. The LPF output is applied to pin 10 of IC203.

The input signal level at pin 11 must be aligned with that at pin 10 so as to subtract the main signal from the 1H delayed signal. This alignment can be done with VR211. The noise component is reversed in its phase, and is added to the main luminance signal from pin 15. The noise-free luminance signal appears at pin 16 of IC203.

#### 5. MAIN DE-EMPHASIS AND NONLINEAR DE-EMPHASIS CIRCUITS

The luminance signal appearing at pin 16 of IC203 is applied to the main de-emphasis circuit.

The main de-emphasis circuit consists of Q235, Q237, C2131, R2166, R2168, C2133, C2134, and C2215. and is used to de-emphasize the high frequency which was emphasized by main emphasis circuit during recording. The output of the main de-emphasis circuit is input to pin 12 of IC202, where the signal is nonlinear de-emphasized to restore the signal to its original condition. The signal then appears at pin 14 of IC202 after passing through a noise canceller within the IC.

# 6. LUMINANCE-CHROMINANCE MIXER CIRCUIT

The luminance signal appearing at pin 14 of IC202 is applied to pin 28. The chrominance signal is input to pin 7 of IC202, where it is mixed with the luminance signal in the mixer within the IC. The mixed video signal appears at pin 5 of IC202.

## 7. VIDEO OUTPUT CIRCUIT

The video signal appearing at pin 5 of IC202 is input to an apperature circuit via Q257, where the high frequency signal response is corrected to flat. The output of the apperature circuit is applied to an amplifier comprised of Q256, Q255, and Q254, whose output is input to Q242. The output of Q242 is applied to the RF converter via an RF equalizer and emitter follower (Q243).

The output of Q242 also branches to the VIDEO OUT jack on the rear panel via another emitter follower (Q244).

# 2-1-5. COLOR SIGNAL RECORDING SYSTEM

# 1. GENERAL

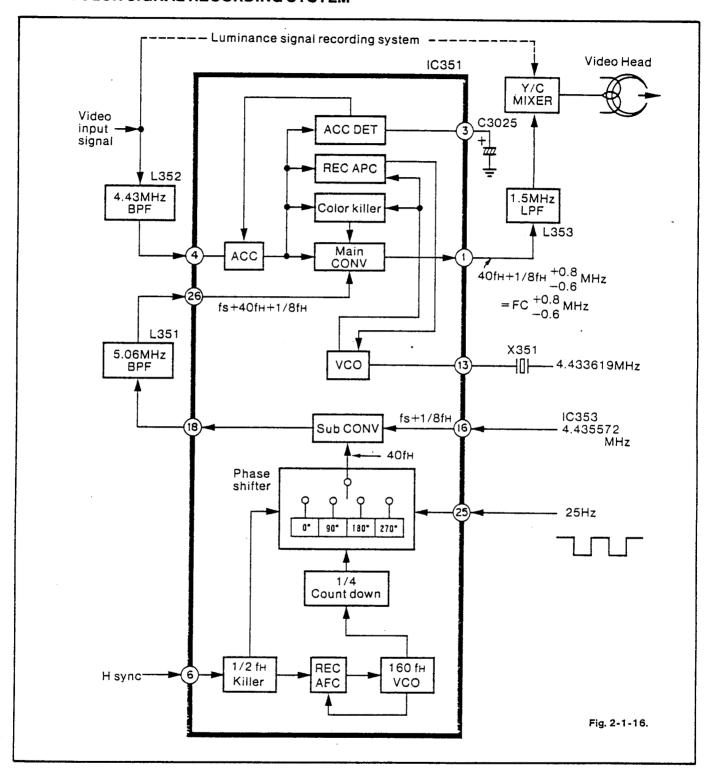

This is direct recording system using a down converted phase shifted color signal. The phase shift system removes color crosstalk which cannot be completely eliminated by the azimuth video heads. Fig. 2-1-16 illustrates a simplified block diagram of this system.

A bandpass filter (BPF) extracts the color component from the input video signal and supplies it to the main converter.

At the same time, the input signal also goes to the horizontal sync separator, which supplies the 15.625kHz (fH) to the multiplier and phase shift circuits. Via the phase shifter, the 40 fH CH-1 track component is supplied directly to the sub converter, but the CH-2 component is delayed in phase 90° every line (1H). A 25Hz rectangular wave synchronized to the video head rotation is used for differentiating between the CH-1 and CH-2 components. Each line is also controlled by the fH input.

The local oscillator produces the color subcarrier frequency 4.433619MHz (Fs) + 1/8 fH single frequency which goes to the sub converter. At the sub converter, the 40 fH and (Fs + 1/8 fH) are frequency converted to become (Fs + 40 fH + 1/8 fH). This is supplied through a highpass filter to the main converter. Also supplied to the main converter are the color signal Fs +0.6 -0.8 MHz and carrier wave (Fs + 40 fH + 1/8 fH). These are down converted to become (40 fH + 1/8 fH +0.8 -0.6 MHz) which through a lowpass filter goes to the mixer for mixing with the FM luminance signal. The result is applied to the video heads.

In other words, the 4.433619MHz (Fc) color subcarrier is converted to a low band of 626.953kHz (40 ft  $\pm$  1/8 ft). The down converted color signal is then recorded directly using the FM luminance signal as AC bias.

# (1) Color crosstalk correction by phase shift system

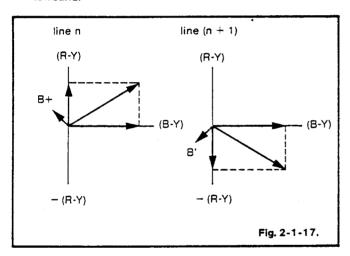

A synchronous quadrature modulation system is employed in which the phase of the color signal R-Y component is reversed every line in order to prevent transmission distortion.

The color signal indicated in Fig. 2-1-17 is converted to a lowband.

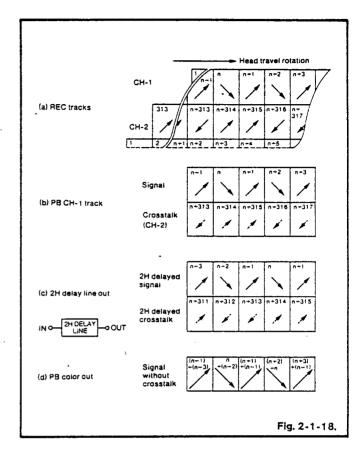

While the CH-1 track component is recorded with phase unchanged, the phase of the CH-2 track component is delayed 90° every line. Fig. 2-1-18 illustrates the principle of this phase shifts system.

In the figure, (a) indicates the phase shifted recording pattern. Since the CH-1 head pattern is not phase shifted, the R-Y component phase becomes inverted every line. The phase of the CH-2 head pattern is delayed every line and this causes its R-Y component phase to become inverted every two lines.

During playback, when the CH-1 head picks up a portion of the CH-2 track signal, this becomes the crosstalk component. Phase shift is not required for the main signal from the CH-1 track, and this output is shown by (b). The dotted arrows indicate the crosstalk component and, as can be noted, the phase reverses every 2 lines.

Passing signal (b) through a 2H delay line yields signal (c). In comparing signals (b) and (c), the main signal phase is the same every line, but the crosstalk phase reverses. Therefore, by mixing signals (b) and (c), the crosstalk component of the adjacent track can be removed to result in the playback color signal (d).

In other words, the color signal can be considered in 2H units. It is recorded by the phase shift system and during playback, the signal through a 2H delay line is mixed to remove crosstalk.

Crosstalk in the playback color signal (d) effectively becomes zero, while the main signal is enhanced to improve S/N. Also, the CH-2 head playback phase is advanced 90° every line (opposite to recording), producing the same effect. A digital type system is used for phase shifting.

# (2) Down converted color subcarrier frequency

The color subcarrier frequency (Fs) can be expressed as:

$$F_S = (n-1/4)f_H + 1/625 f_H = 283.75 f_H + 25 H_Z$$

$$(n = 284) = 4.433619 MH_Z$$

A line offset system is used in which the subcarrier phase is delayed 90° every line. This avoids serious color noise when the color signal is displayed on a monochrome TV receiver. 25Hz is added in order to prevent crosscolor.

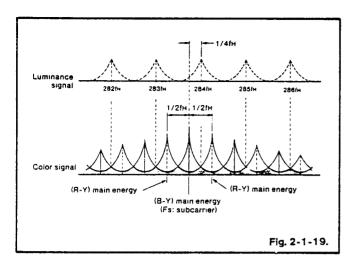

As indicated in Fig. 2-1-18, the phase of the color signal R-Y component is inverted every horizontal line to compose a synchronous quadrature modulated signal. Fig. 2-1-19 shows this color signal spectrum.

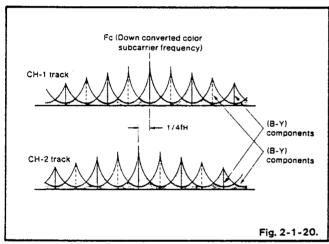

In the phase shift system, the CH-1 component of the down converted color signal is distributed at 1/2 fH intervals centered on the Fc (down converted color subcarrier) component. The CH-2 track component is delayed in phase 90° every line, deviated by 1/4 fH, and distributed at 1/2 fH intervals centered on Fc. This spectrum is shown in Fig. 1-1-20.

The FM luminance and down converted color signals are mixed to become the recording current. When recorded and played back using magnetic tape, which processes 3-dimensional distortion and nonlinearity, interference in the form of Fo + 2Foc (Fo: FM carrier; Foc: down converted color signal) becomes introduced and cannot be ignored. When the 2Foc component is detected and demodulated, beat becomes produced with respect to the luminance signal and appears in the picture. Therefore, as with the color signal, Fc (down converted color subcarrier frequency) must be selected so that the 2Foc component becomes 1/4 offset in relation to the luminance signal, i.e.:

$$2Fc = \frac{2n-1}{4} fH$$

$$Fc = \frac{2n-1}{8} fH = \frac{321}{8} fH = 40 fH + \frac{1}{8} fH (n = 161)$$

$$= 625 + 1.953 = 626.953 kHz$$

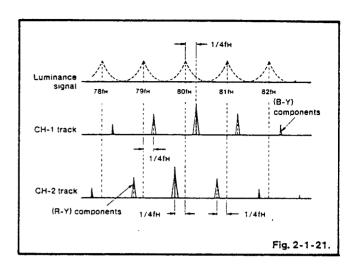

When Fc is determined at (40 fH  $\pm$  1/8 fH), the spectrum of the CH-1 track B-Y component appears at (nfH  $\pm$  1/8fH) and the R-Y component at (nfH  $\pm$  3/8 fH). In the CH-2 track distribution, B-Y appears at (nfH  $\pm$  1/8 fH) and R-Y at (nfH  $\pm$  5/8 fH).

Fig. 2-1-21 shows the 2Fpc component spectrum with respect to the playback luminance signal at this time.

The 2Fpc components for both CH-1 and CH-2 become 1/4 line offset with respect to the luminance signal and thereby visually reduced. The 626.953 value was selected for both reducing noise and in consideration of color bandwidth.

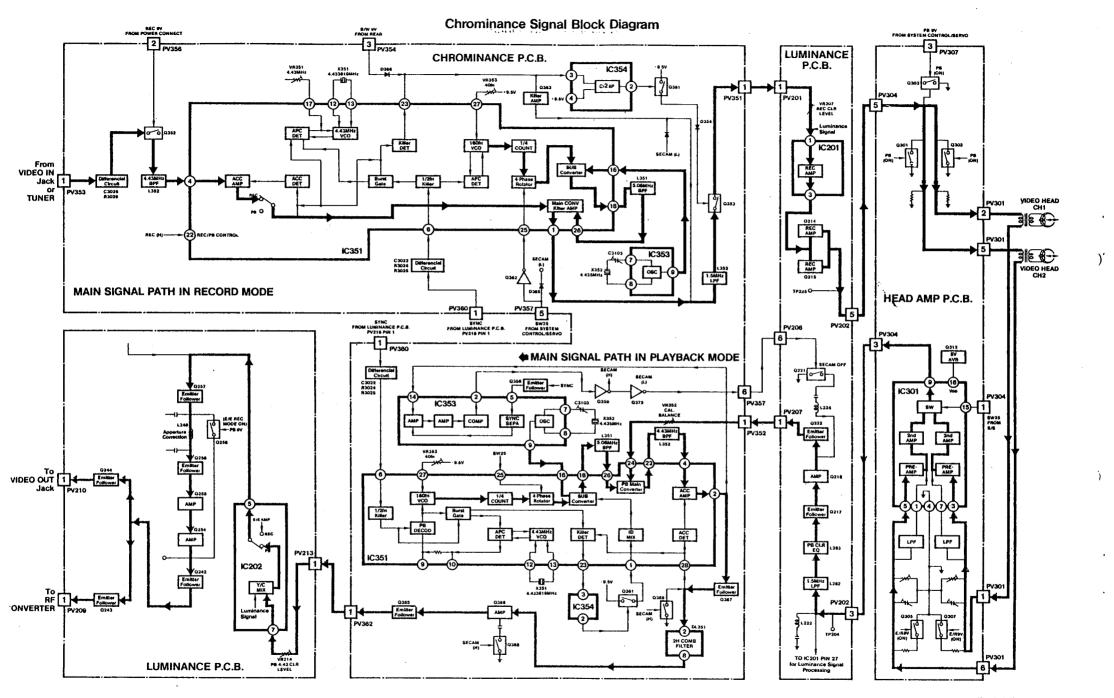

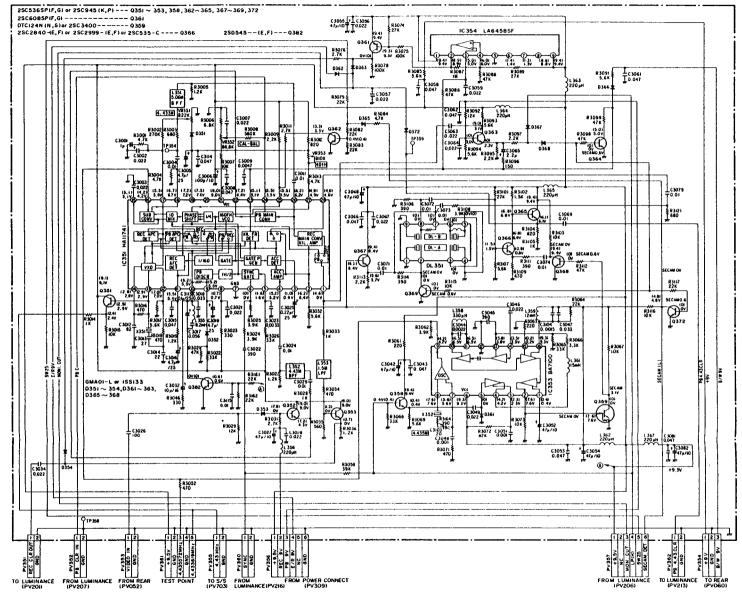

We have look at the principle of chrominance signal processing in some detail. The following sections describe the circuit functions according to signal flow. See Fig. 2-1-5 Chrominance Signal Block Diagram. The upper section in Fig. 2-1-5 shows chrominance signal path in recording mode and lower section shows playback mode.

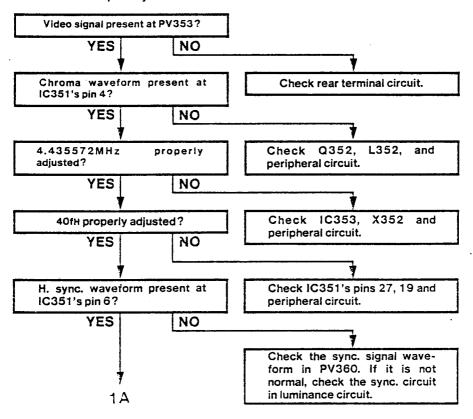

# 2. 4.43MHz BAND-PASS FILTER (BPF) AND ACC CIRCUIT

The input video signal is applied to a differential circuit composed of C3026 and R3029 to remove the vertical sync component from it. The output of the differential circuit is input to a 4.43MHz BPF, where only the chrominance signal is extracted from the video signal. The output of the BPF goes to pin 4 of IC351.

The 4.43MHz chrominance signal is input an ACC amplifier and REC/PB switch, where the burst signal is extracted from it by burst gate pulse. The burst signal is applied to an ACC detector circuit, where a detection output corresponding to the burst signal level is taken out to control the ACC amplifier gain. As a result, the ACC amplifier output level variation is suppressed below ±0.5dB for an input level variation of ±6dB.

# 3. 4.433619MHz VOLTAGE CONTROLLED OS-CILLATOR (VCO)

The 4.433619MHz oscillation is obtained by X351 crystal oscillation circuit. The oscillation frequency is adjustable with VR351 connected to pin 17 of IC351. The Rec APC circuit functions to lock the 4.433619MHz oscillation output phase with that of the burst signal from the ACC amplifier. This signal is also supplied to the killer detector.

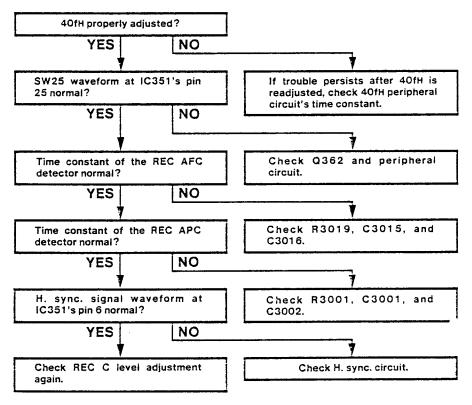

#### 4. 40fh SIGNAL GENERATION

After synchronization and separation by IC202 inside luminance P.C.B., the synchronization signal passes through the differential circuit of C3022, R3024 and R3025, and it becomes horizontal sync signal and equalizing pulse.

These signals are fed to IC351 pin 6, and is input to 1/2fH killer circuit where the equalizing pulse is removed. The remaining horizontal sync signal (fH) is input to rec AFC detector circuit which controls the phase of 160fH VCO.

To synchronize the 160fH VCO with the horizontal sync signal, the frequency of VCO is divided by 160 and its phase is compared with the horizontal sync signal. The resulting error voltage is used to phase correct the 160fH VCO. The circuit required is called AFC loop.

VCO. The circuit required is called AFC loop.

The 160fh pulse is divided by 1/4 divider to produce the 40fh pulse. The phase of 40fh pulse is delayed by 90° every 1H for CH2 while the phase for CH1 is unaltered. The resulting 40fh signal is supplied to subconverter.

## 5. 4.435572MHz OSCILLATOR

The 4.435572MHz oscillator consists of a crystal element (X352) and an oscillator circuit (IC353). The output of the oscillator is output from IC353 pin 9, and is input to the subconverter via pin 16 of IC351.

## 6. SUBCONVERTER

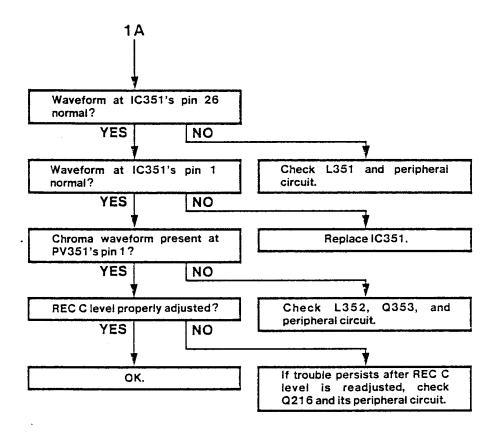

The 4.435572MHz and 40fH (625kHz) signals are applied to the subconverter, where they are mixed to produce a 5.06MHz and 3.81MHz signals, which are output from pin 18 of IC351. The signal then goes to a 5.06MHz BPF (L351), where only the 5.06MHz signal is extracted, and is input to pin 26 of IC351.

#### 7. DOWN-CONVERTED CHROMINANCE SIGNAL

The 5.06MHz signal applied to pin 26 of IC351 is supplied to a main converter, where it is mixed with the 4.433619MHz chrominance signal from the ACC amp. The output of the main converter appears at pin 1 of the IC351.

The output signal at pin 1 contains two frequencies of 626.9kHz and 9.49MHz. This output is fed to a 1.5MHz LPF (L353), where a 626.9kHz down-converted chrominance signal is extracted. This signal is recorded on tape using the FM luminance signal as an AC bias.

# 2-1-6. CHROMINANCE SIGNAL PLAY-BACK SYSTEM

#### 1. GENERAL

The color signal playback system performs essentially the opposite function as the recording system. In addition, however, important corrections must be performed for color signal frequency and phase errors introduced by variations in tape speed and head rotation, and elasticity of the tape.

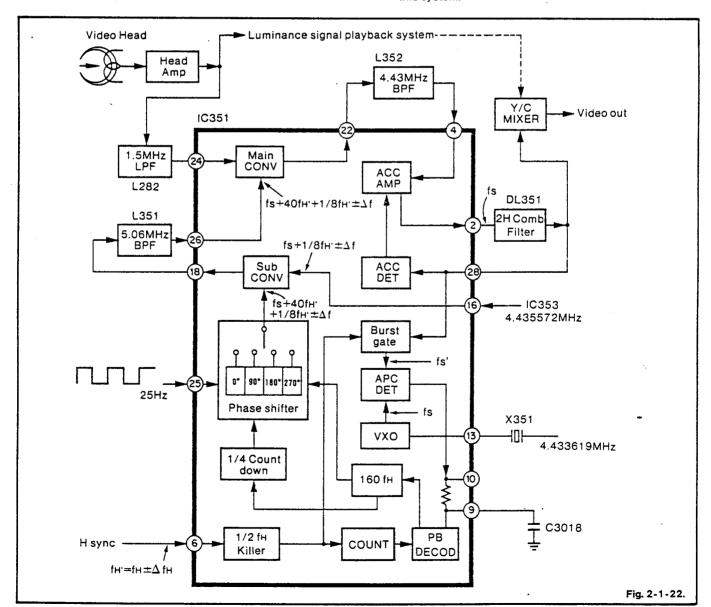

Fig. 2-1-22 indicates an abbreviated block diagram of this system.

Though a lowpass filter, the down converted color signal goes to the main converter. At this time, the down converted color subcarrier (Fc) contains an error component (40 fh'  $\pm$  1/8 fh'  $\pm$   $\Delta$ f) due to mechanical factors of the heads and tape. fh' varies with the tape speed as fh'  $\pm$   $\Delta$  fh'.  $\Delta$ f is the instantaneous error caused by head rotation irregularities and tape elongation and contraction.

The 40 fh frequency deviation component is compensated by supplying the video output signal to the horizontal sync separator, multiplier and phase shifter, and 40 fh to the sub converter. This forms the AFC (automatic frequency compensator) loop.

In the APC (automatic phase compensator) loop, the 1/8 fH'  $\pm$   $\Delta f$  phase error component is compensated by comparing the burst component of the up converted playback color signal with the subcarrier frequency from the local oscillator and APC detector. A variable crystal oscillator (VXO) produces (Fs + 1/8 fH'  $\pm$   $\Delta f$ ) which goes to the sub converter. As a result, (Fs + 40 fH' + 1/8 fH'  $\pm$   $\Delta f$ ) is supplied as the main converter carrier input from the sub converter through a highpass filter.

By frequency conversion with Fc, the color subcarrier frequency of 4.433619MHz, which is free from frequency and phase deviations, becomes obtained through a bandpass filter. In the opposite manner as with recording, the phase shifter advances the CH-2 track phase 90° every line and 40 fH is supplied to the sub converter. The playback color signal through the main converter and bandpass filter is applied to a 2H delay line for removing crosstalk. Characteristics of the low-pass and bandpass filters are the same as those for recording.

At the mixer, the playback color and luminance signals are mixed to become the video output signal.

# 2. CHROMINANCE AND LUMINANCE SEPARATION

The down-converted chrominance signal is extracted from the envelope output of the video head by a 1.5MHz low-pass filter (L282) inside the luminance P.C.B. The output of the LPF is input to pin 24 of IC351 inside the chrominance P.C.B. via emitter follower (Q217, Q218, Q222).

# 3. 4.435572MHz SIGNAL GENERATION

Similar to the record mode, a 4.435572MHz signal is generated by a crystal-controlled oscillator, IC353 with X352. The signal is supplied from pin 16 of IC351 to the subconverter. The oscillating frequency is adjustable with a trimmer capacitor (C3103).

#### 4. ID CIRCUIT

If phase switching point in playback chrominance signal does not match that in recording, a 180° of discontinuity will occur in the playback down-converted chrominance signal. This will cause a color flicker appearing in the upper section of the screen. The ID circuit is used to detect this discontinuity. The killer detector inside IC351 also functions as the ID detector.

The ID detector compares the 4.433619MHz VCO output with the burst signal contained in the playback chrominance signal. If a discontinuity occurs, the detector makes the same decision as in the monochrome mode, to generate a High level pulse at pin 23 of IC351.

This positive ID pulse is input to the emitter of Q363, and is output at its collector also as a positive pulse. The ID pulse then goes to pin 1 of IC351, drives a 40fH inverter circuit to eliminate 180° of the discontinuity.

# 5. 40fh GENERATOR

The synchronization signal is separated from the play-back luminance signal by the sync separation circuit inside IC202, and is output from IC202 pin 3. This sync signal passes the differencial circuit (C3022 and R3025) and becomes horizontal sync signal. This signal is then supplied to IC351 pin 6.

The horizontal sync signal controls the phase of 160fh VCO. The 160fh is frequency divided by four, and the 40fh is generated by the 4-phase rotator circuit.

# 6. SUBCONVERTER CIRCUIT

In the same way as at the time of recording, the 4.435572MHz from IC353 is supplied to pin 16 of IC351. This signal and 40fH from the 4-phase rotator circuit are input to subconverter where they are mixed. The mixed output appears at pin 18 of IC351.

#### 7. PB MAIN CONVERTER

The subconverter output apperating at pin 18 of IC351 goes through the 5.06MHz BPF (L351) where only the 5.06MHz frequency component is extracted.

This 5.06MHz is input to PB main converter via IC351 pin 26, while the down-converted playback chrominance signal (627 kHz) is also input to PB main converter via pin 24 of IC351.

Two signals are mixed with PB main converter and output from pin 22 of IC351.

# 8. ACC CIRCUIT

The PB main converter output appearing at pin 22 of IC351 is applied to a 4.43MHz BPF (L352), where its 4.43619MHz frequency component (chrominance signal of TV signal) is extracted. The output of the BPF is input to pin 4 of IC351 and enters the ACC amplifier. The output of the ACC amplifier appears at pin 2 of IC351, and goes to a 2H comb filter via an emitter follower (Q367). The 2H comb filter eliminates crosstalk from adjacent channels, and is input to the following amplifier (Q366).

For the details of the principle of crosstalk removal, refer to section 2-1-5.

The signal is sent to emitter follower (Q367) and then input to pin 28 of IC351, where it is coupled to an ACC detector circuit within the device. The ACC detector controls the ACC amplifier gain. Thus, an ACC loop is formed to regulate the chrominance signal level to a constant.

# 9. CHROMINANCE OUTPUT

The chrominance signal from the emitter follower (Q365) is input to IC202 pin 6 within the luminance circuit via PV362 pin 1 and PV213 pin 1.

The chrominance signal is mixed with the luminance signal in the mixer within IC202. The resulting TV signal is supplied to the RF converter and VIDEO OUT jack.

The VTR is capable of recording and playing the SECAM B/G standard signals.

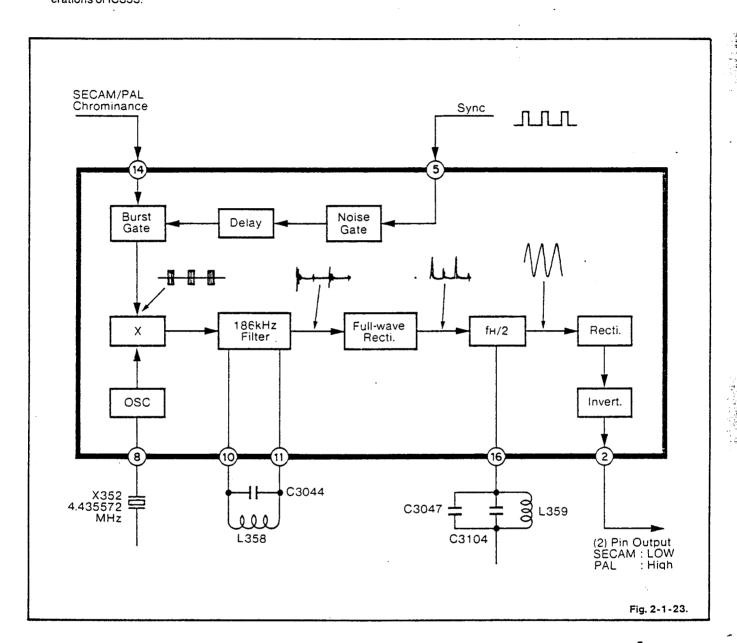

IC353 discriminates PAL/MESECAM signals. Figure 2-1-23 shows a block diagram illustrating the internal operations of IC353.

The color burst signal for the MESECAM signal has frequencies of 4.25MHz and 4.40625MHz, and is supplied at 1H intervals. The burst signal frequency is multiplied by the output frequency of a 4.435572MHz oscillator within the IC. If a 4.435572MHz filter (L358 and C3044) is used as a load, 4.435572MHz - 4.25MHz = 186kHz is obtained at the load. The output of the filter is subject to full-wave rectification to take out the fH/2 component (resonant circuit composed of L359, C3104 and C3047). The fH/2 component is rectified. The low output appears at pin 2 of IC353 via an inverter.

For the PAL signal, the 186kHz signal is not available as the 4.25MHz component does not exist. So pin 2 of

IC353 remains at High.

The noise gate logic prevents the burst gate to be opened or closed at random due to sync signal disturned when the field strength is weak.

Since the MESECAM chrominance signal is an FM signal, it has no crosstalk from adjacent channels. It is not necessary, therefore, to shift the signal phase at 1H intervals, as is the case with the PAL signal. The 25Hz pulse is set to High by turning Q362 off. When pin 25 of IC351 is set to High, rotation of 40fH stops.

Playback of MESECAM signal requires no crosstalk removal using a 2H comb filter. Q369 is turned on to block the chrominance signal from the 2H comb filter.

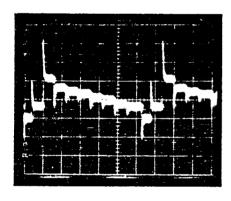

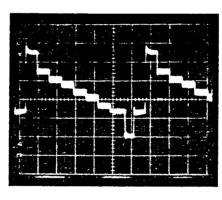

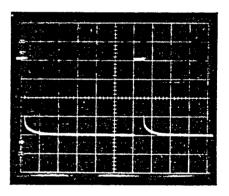

# 2-1-8. VIDEO WAVEFORMS

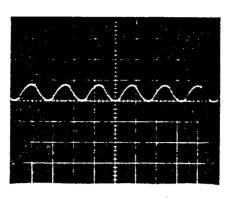

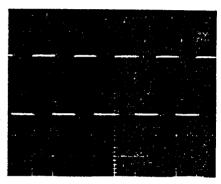

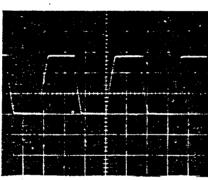

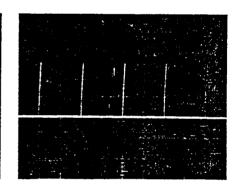

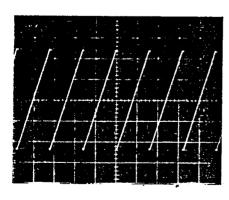

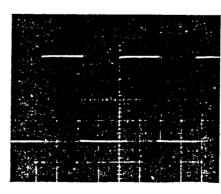

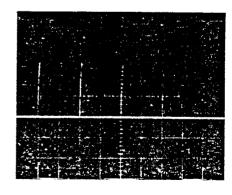

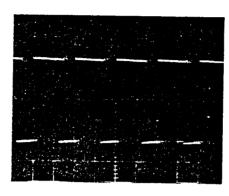

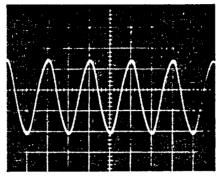

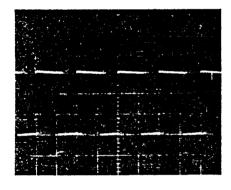

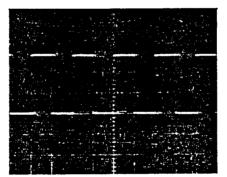

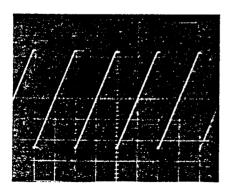

TP213 EE 200mV/10μsec div.

IC202 PIN 24 PB 1V/10μsec div.

IC202 PIN 24 REC 200mV/10μsec div.

IC202 PIN 13 PB 100mV/10μsec div.

IC202 PIN 13 REC  $100 \text{mV}/10 \mu \text{sec div.}$

IC201 PIN 18 REC 200mV/10µsec div.

TP203 REC 200mV/10μsec div.

TP202 REC  $200 \text{mV}/10 \mu \text{sec div.}$

TP225 REC 1V/10μsec div.

TP204 PB 10mV/10μsec div.

TP226 PB 50mV/10μsec div.

TP201 PB 100mV/10μsec div.

TP212 PB 50mV/10 $\mu$ sec div.

IC202 PIN 14 PB 200mV/10μsec div.

$1C202 PIN 3 REC 2V/10\mu sec div.$

IC202 PIN 7 PB 50mV/10μsec div.

IC202 PIN 5 REC 500mV/10µsec div.

IC202 PIN 5 EE 200mV/10μsec div.

IC351 PIN 6 REC 1V/10μsec div.

IC351 PIN 4 PB 100mV/10μsec div.

IC351 PIN 4 REC 50mV/10µsec div.

IC351 PIN 1 REC 200mV/10µsec div.

IC351 PIN 2 PB 500mV/10μsec div.

Q353 EMITTER REC 50mV/10 $\mu$ sec div.

IC351 PIN 24 PB 100mV/10μsec div.

IC351 PIN 26 PB 50mV/10µsec div.

IC351 PIN 26 REC 50mV/10µsec div.

Q365 EMITTER PB  $200 \text{mV}/10 \mu \text{sec div.}$

PV362 PIN1 PB 200mV/10µsec div.

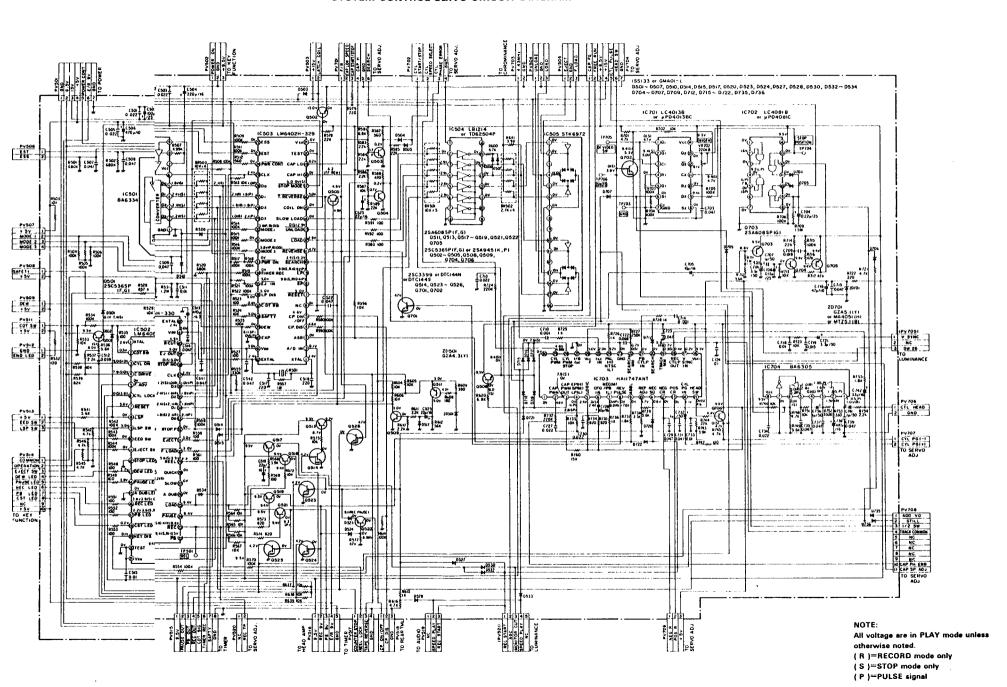

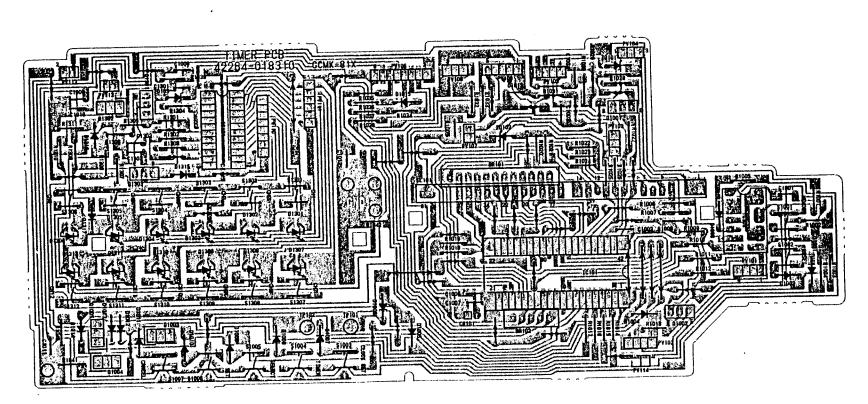

# 2-2. SYSTEM CONTROL CIRCUIT

# 2-2-1. GENERAL DESCRIPTION

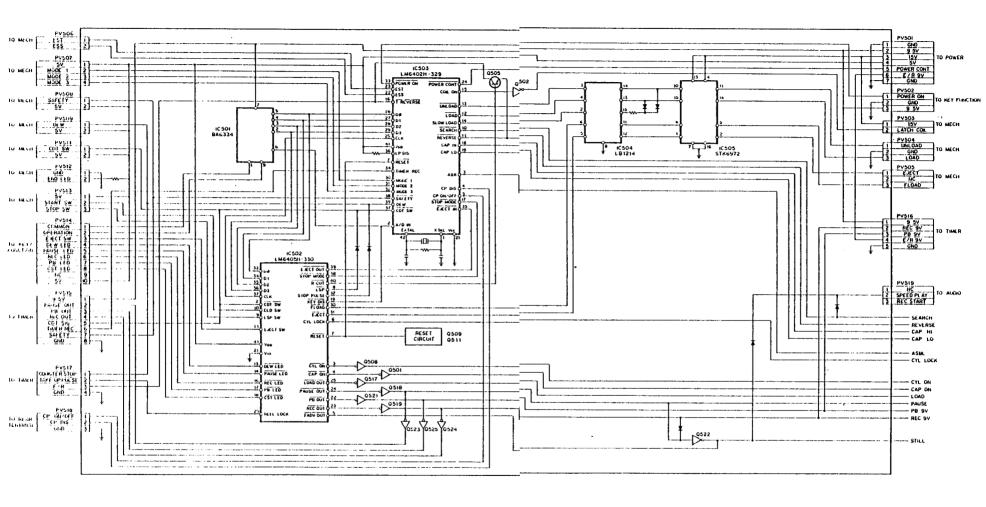

## 1. FEATURES

- The system control is a 2-clip configuration of the MAIN CPU and the SUB CPU of the N-ch MOS 42-pin. The SUB CPU is controlled by the transferred data from the MAIN CPU.

- The operation of the mechanism is directly controlled by the MAIN CPU with the mode select switch and the front loading mechanism being controlled by the SUB CPU.

- 3) When the power is switched ON, the initialize operation controls the loading motor so that the mode select switch input is placed in the stop mode. If the tape is not loaded into the proper position in the front loading mechanism (stopped in the middle), the tape is ejected.

- 4) During unloading and ejecting, if the loading motor or the front loading motor is mechanically locked due to mechanical trouble, the motor power is automatically cut to prevent motor and drive IC damage.

- 5) During eject, tape slack is removed.

- 2. BLOCK DIAGRAM (See Fig. 2-2-1)

# 2-2-2. INPUT/OUTPUT SIGNALS DESCRIPTION

# 1. MAIN CPU INPUT SIGNALS

1) A/D IN Pin No. 2

This input is determined by the function button being pressed (PB, REC, etc., excluding EJECT) as each button has a different resistance. The voltages generated by pressing the function buttons are A/D converted.

2) MODE 1-3 Pins No. 30-32 This input expresses the mechanism modes such as the STOP mode, PB mode etc., as well as controlling the operational timing of the mechanism during shifts from

one mode to another.

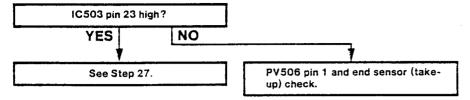

3) TAPE END DETECTION

ESS Pin No. 22

Supply reel side tape end detection. Active with the high input.

EST Pin No. 23

Take up reel side tape end detection.

Active with the high input.

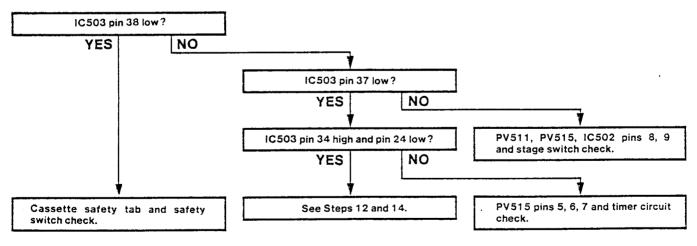

4) MECHANISM DETECTION SW

CDT/SW Pin No. 37

Detects the cassette when the cassette holder is in down position. Input is low when the SW becomes active.

SAFETY Pin No. 38

If the safety tab has been removed, the input becomes low and does not allow REC.

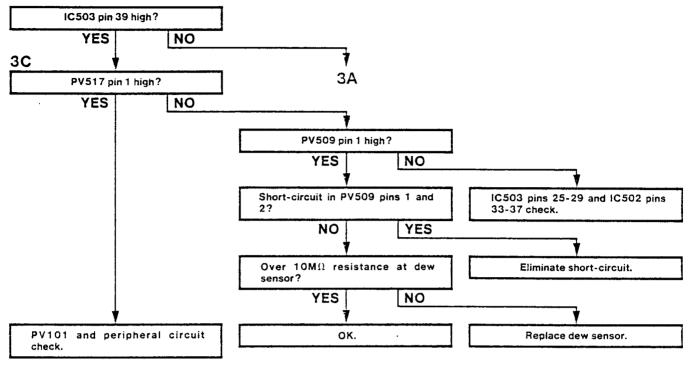

## 5) TROUBLE DETECTION

DEW Pin No. 39

Input becomes high when dew condensation is detected inside the set; the set is placed in the STOP mode. At the same time, the DEW LED blinks and does not allow key inputs. When the input becomes low, the blinking stops and key inputs are allowed.

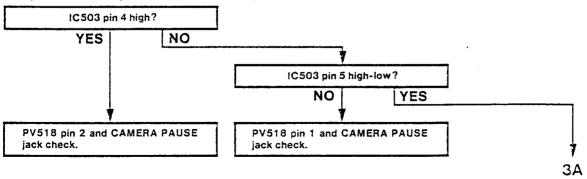

## 6) CAMERA CONTROL

CP DIS Pin No. 4

If input is high, the control input signals from the camera are not accepted.

CP ON/OFF

Pin No. 5

If input is high when the CP DIS input is low, the pause mode is established; if input is low, the pause mode is disengaged.

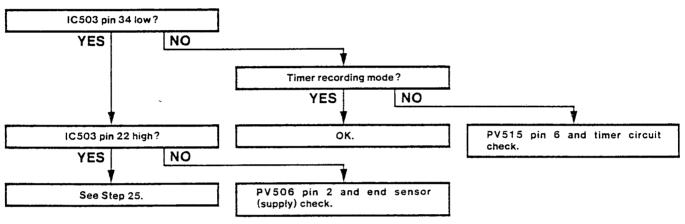

7) TIMER INPUT

TIMER REC Pin No. 34

The set is placed in the REC mode if the REC conditions are met and the input is high. At this time, key inputs are not allowed.

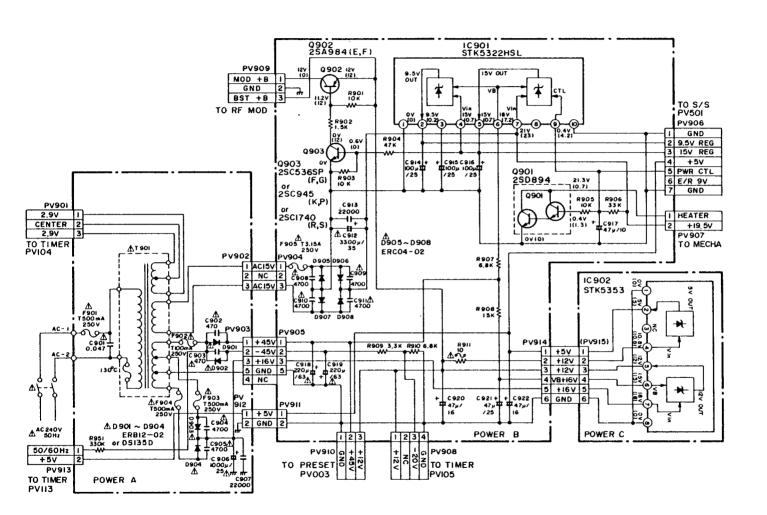

# 8) POWER CONTROL INPUT

PWR ON Pin No. 33

Input becomes low when the PWR ON SW is pressed;

the PWR CONT output becomes low and power is sun-

the PWR CONT output becomes low and power is supplied to all circuits.

9) EJECT IN Pin No. 35

Input becomes low when the eject key is pressed; other key inputs are blocked.

# 2. MAIN CPU OUTPUT SIGNALS

# 1) CAPSTAN MOTOR CONTROL

CAP LO Pin No. 19

Rotates the capstan motor at low speed to remove the

tape slack.

CAP HI Pin No. 18

Rotates the capstan motor at high speed during FF and

REW.

REVERSE Pin No. 11

Runs direction signal for the capstan motor. The motor runs in forward direction (clockwise) when this is high and in reverse direction (counterclockwise) when low.

SEARCH Pin No. 10

Rotates the capstan and cylinder motors at high speed when this is low, and effective in cue or review operation.

## 2) LOADING MOTOR CONTROL

LOAD Pin No. 12

When output is low, the loading motor is driven in the CCW (loading) direction.

UNLOAD Pin No. 13

When output is low, the loading motor is driven in the CW (unloading) direction.

SLOW LOAD - Pin No. 14

When output is high, the motor speed is reduced to control the mode select switch operation precisely.

3) COIL ON Pin No. 15

When output is high, the coil is energized and reel brake is held in released condition.

4) ASR Pin No. 3

Outputs assemble record signal when changing from pause to record mode.

# 5) TAPE COUNTER CONTROL

T REVERSE Pin No. 16

When output is low, it commands the tape counter to count down. (with R CUT correction)

## 6) STOP MODE

Pin No. 17

Outputs a signal to recognize the SUB CPU that the mechanism is in STOP mode. When output is low, the mechanism is in the STOP mode.

## 7) DATA TRANSFER

CLK Pin No. 25

The clock signal when transferring data to the SUB CPU.

D0-D3 Pins No. 26-29

Data transfer bus to the SUB CPU.

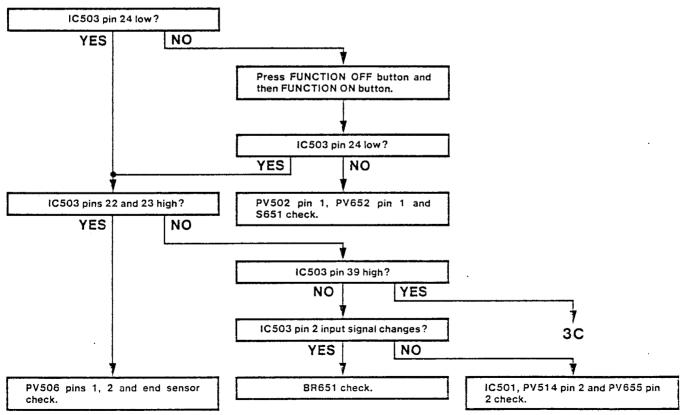

#### 8) POWER CONTROL

**PWR CONT**

Pin No. 24

When the PWR IN input is low, a low is output to the power circuit, and +9.5V, +15V are supplied.

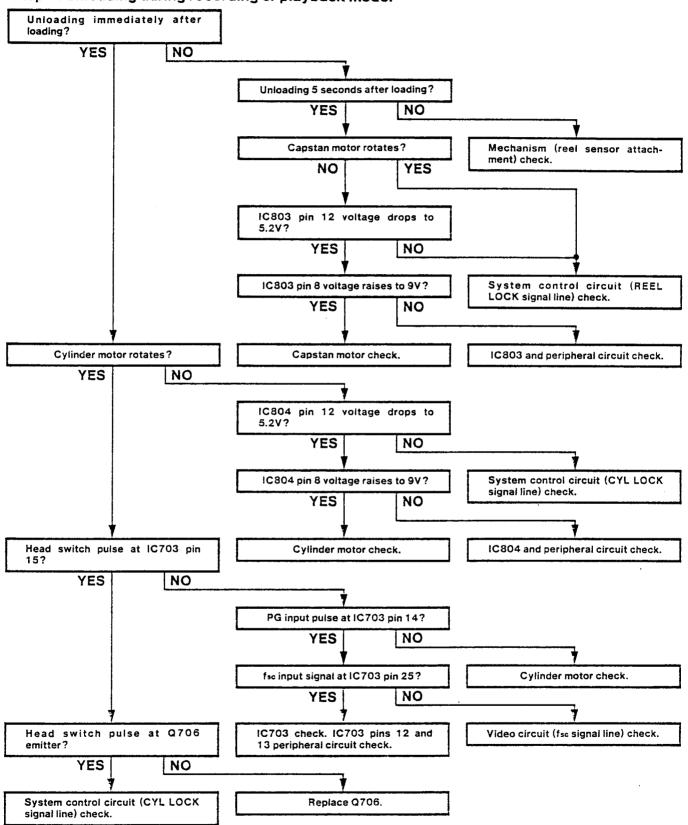

#### 3. SUB CPU INPUT SIGNALS

#### 1) TROUBLE DETECTION

CYL LOCK Pin No. 6

While the VCR is operating, the input pulse frequency is 30 Hz. When the STOP button is pressed, the input pulse frequency changes to 15 Hz and the VCR is automatically placed in the STOP mode. When the VCR stops, the input pulse frequency changes to 0 Hz. Check is started when loading is completed.

REEL LOCK Pin No. 29

Drive detection of the take up reel.

The set is placed in the stop mode if a drive signal is not received from the take up reel for 1.5 seconds during FF, REW, and 7 seconds during PB, REC. Check is started when loading is completed.

## 2) MECHANISM DETECTION SW

LSPSW Pin No. 9 Input is high when the cassette holder is in down

input is high when the cassette holder is in down position.

**EED SW**Input is high when the cassette holder is up; input be-

comes low when the tape is inserted.

CDT SW

Pin No. 2

Input becomes low if the cassette holder is in down position and the cassette detection SW becomes active.

#### 3) EJECT SW Pin No. 11

Input becomes high when the EJECT key is pressed.

# 4) STOP MODE Pin No. 38

Recives an input from the MAIN CPU. When the input is low, the mechanism is in the STOP mode.

#### 5) DATA TRANSFER

CLK Pin No. 37

Clock signal for data transfer from the MAIN CPU.

D0-D3 Pins No. 33-36

Data transfer bus from the MAIN CPU.

## 4. SUB CPU OUTPUT SIGNALS

#### 1) LED INDICATORS

PB LED Pin No. 17

During PB or REC mode, low is output and the PB LED lights up.

REC LED Pin No. 16

During REC mode, low is output and the REC LED lights up.

PAUSE LED Pin No. 14

During STILL, REC or PAUSE, low is output and the PAUSE LED lights up.

DEW LED Pin No. 13

When dew is detected, high and low are output alternately and the DEW LED blinks.

CST LED Pin No. 18

When the CDT SW input is low, low is output and the TAPE IN lights up.

Pin No. 22

# 2) SERVO CIRCUIT CONTROL

**PBOUT**

|            | Low output during DP                              |  |

|------------|---------------------------------------------------|--|

| Pin No. 23 | Low output during PB. REC OUT                     |  |

| D! N 0.4   | Low output during REC.                            |  |

| Pin No. 24 | PAUSE OUT Low output during PAUSE.                |  |

| Pin No. 25 | LOAD OUT                                          |  |

| Pin No. 4  | Low output during loading.  C DRIVE               |  |

| Pin No. 3  | Low output during capstan motor rotation.  CYL ON |  |

| FIII NO. 3 | Low output during cylinder motor rotation.        |  |

| Pin No. 5  | FADVOUT                                           |  |

|            | High output during STILL.                         |  |

|            |                                                   |  |

# 3) EJECT OUT Pin No. 39

Output becomes low when the EJECT key is pressed and informs the main microcomputer that the mechanism should continue eject operations. Output returns to high after completing the eject sequence.

## 4) KEY DIS Pin No. 19

Holds the A/D IN input to low during front loading and eject, to prohibit key inputs.

# 5) STOP PULSE Pin No. 32

Makes a pulse output when the EJECT key is pressed, to place the set in the STOP mode.

# 6) FRONT LOADING MOTOR CONTROL

FLOAD Pin No. 30

When output is low, the front loading motor is driven in the CCW (front loading) direction.

EJECT Pin No. 31

When output is low, the front loading motor is driven in the CW (eject) direction.

# 7) LSP Pin No. 8

Outputs a low, high inverted LSP SW input signal.

# 8) R CUT Pin No. 40

This signal controls the T REVERSE, which commands the reel drive direction of the tape counter.

Fig. 2-2-1

# 2-2-3. CIRCUIT DESCRIPTION

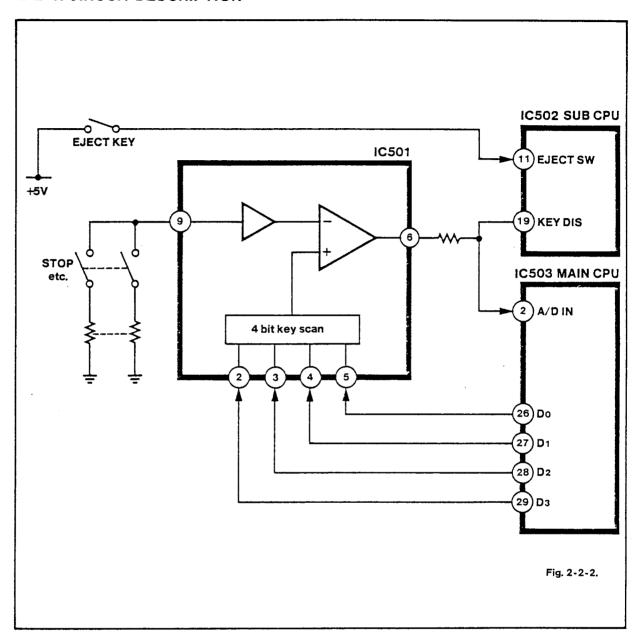

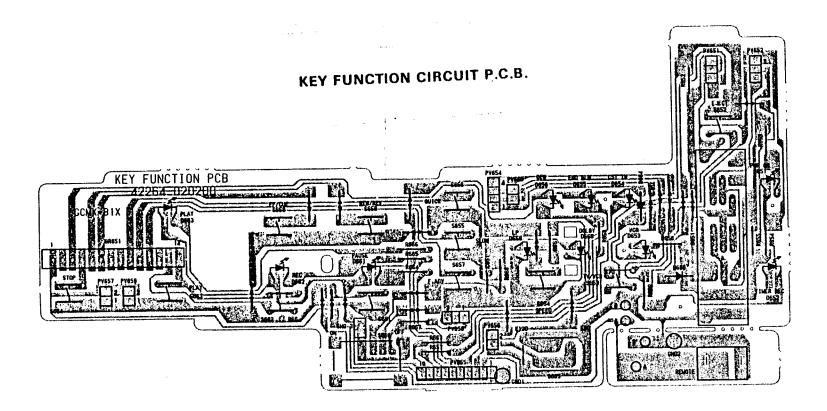

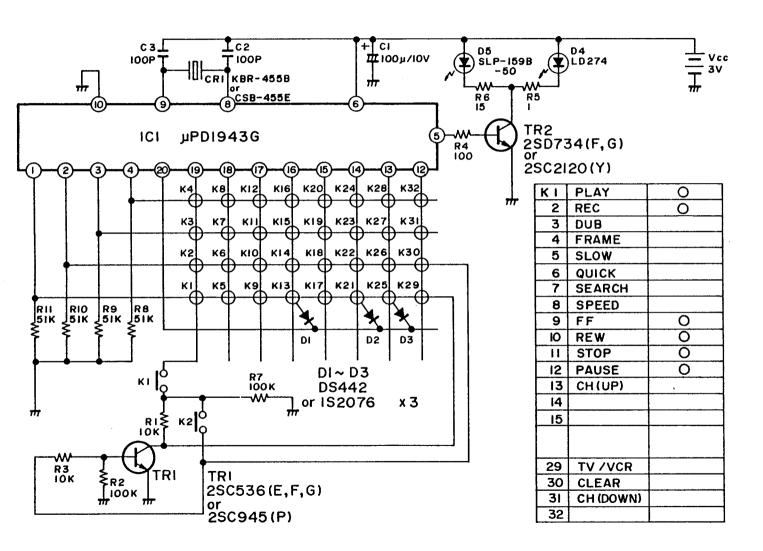

# 1. INPUT KEY DETERMINATION CIRCUIT (See Fig. 2-2-2 and 2-2-3)

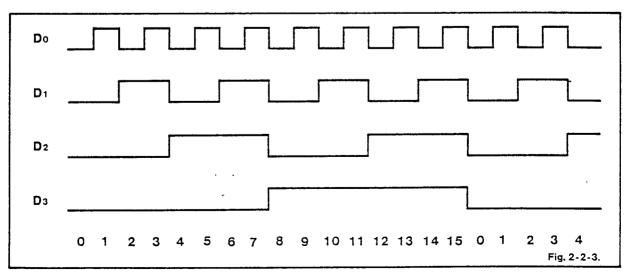

When the OPERATION button is pressed on the front panel, IC502 pin 11 becomes high and the input is accepted. When buttons other than the OPERATION button are pressed, voltage corresponding to the respective button appears at IC501 pin 9, and the pin 6 output changes from low to high. When this output change is sent to the MAIN CPU IC503 pin 2, the outputs from IC503 pins 26-29 commence the count up operations, as shown in the timing chart. These are sent to IC501 pins 5-2, generating a step voltage at the non-inverted input of the built-in operational amplifier of IC501.

The voltage appearing at IC501 pin 9 is sent to the inverted input of the operational amplifier and is compared with the step voltage. This comparison is continued until the output from IC501 pin 6 changes from high to low.

When IC503 pin 2 input detects the change from high to low, the depressed button is identified according to the MAIN CPU program. The relationships between the D3-D0 count value and the input buttons are shown below. (See Table 2-2-1.)

| CODE | Dз | D2 | D1  | Do  | OPERATION |

|------|----|----|-----|-----|-----------|

| 0    | 0  | 0  | 0   | 0   |           |

| 1    | 0  | 0  | 0   | 1   | PB        |

| 2    | 0  | 0  | 1 - | 0   | REC       |

| 3    | 0  | 0  | 1   | 1   |           |

| 4    | 0  | 1  | 0   | . 0 |           |

| 5    | 0  | 1  | 0   | 1   |           |

| 6    | 0  | 1  | 1   | 0   |           |

| 7    | 0  | 1  | 1   | 1   |           |

| 8    | 1  | 0  | 0   | 0   |           |

| 9    | 1  | 0  | 0   | 1   | FF/CUE    |

| 10   | 1  | 0  | 1   | 0   | REW/REV   |

| 11   | 1  | 0  | 1   | 1   | STOP      |

| 12   | 1  | 1  | 0   | 0   | SPEED     |

| 13   | 1  | 1  | 0   | 1   |           |

| 14   | 1  | 1  | 1   | 0   | PAUSE     |

| 15   | 1  | 1  | 1   | 1   |           |

Table 2-2-1.

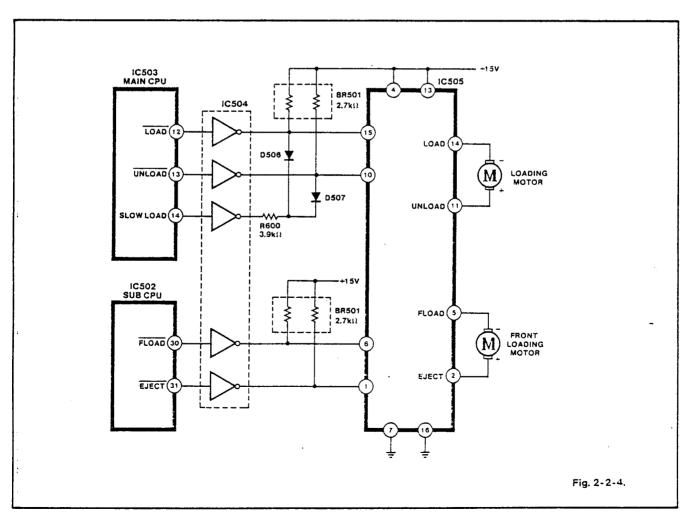

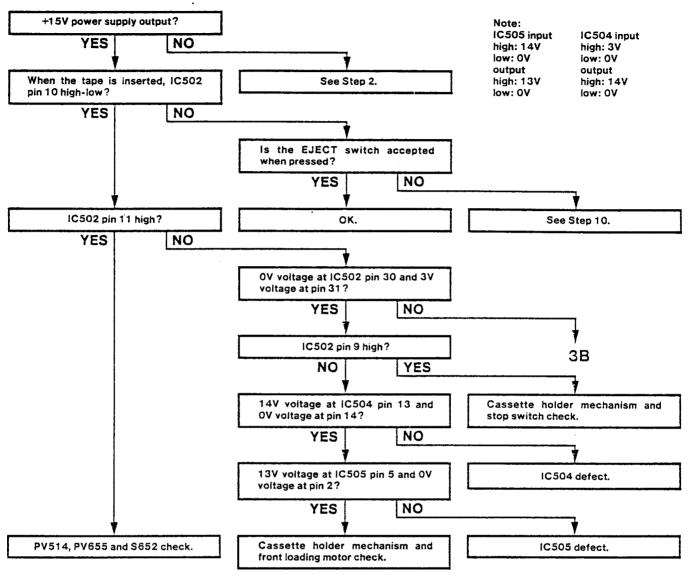

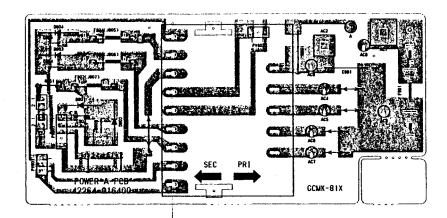

# 2. LOADING MOTOR, FRONT LOADING MOTOR DRIVE CIRCUIT (See Fig. 2-2-4)

#### 1) LOADING

When the IC503 pin 12 output is low and pin 13 output is high, the IC505 pin 14 output becomes approximately 13V and pin 11 output becomes 0V. The loading motor is driven in the CCW direction, placing the mechanism in the loading mode.

#### 2) UNLOADING

When the IC503 pin 13 output is low and pin 12 output is high, the IC505 pin 11 output becomes approximately 13V and pin 14 output becomes 0V. The loading motor is driven in the CW direction, placing the mechanism in the unloading mode.

#### 3) SLOW LOAD

When the IC503 pin 14 output becomes high, the terminal voltage of the loading motor is determined by comparing the various elements of BR502 and R600 and becomes approximately 8V for both loading and unloading. This is used to increase the detection precision of the mode select SW.

# 4) FRONT LOADING

When the IC502 pin 30 output is low and pin 31 output is high, the IC505 pin 5 output becomes approximately 13V and pin 2 output becomes 0V. The front loading motor is driven in the CCW direction, placing the mechanism in the front loading mode.

#### 5) EJECT

When the IC502 pin 31 output is low and pin 30 output is high, the IC505 pin 2 output becomes approximately 13V and pin 5 output becomes OV. The front loading motor is driven in the CW direction, placing the mechanism in the eject mode.

#### 3. LATCH COIL DRIVE CIRCUIT

When the IC503 pin 15 becomes high, Q502 conducts, the latch coil is energized, and the reel brake is held in released condition.

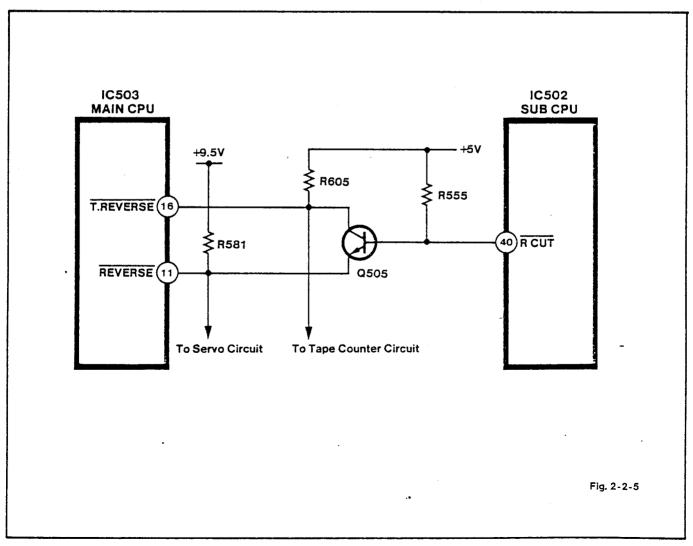

# 4. TAPE COUNTER COUNT UP / DOWN COMMANDS (See Fig. 2-2-5)

The T REVERSE output makes a high or low signal output to the tape counter after being corrected by the logic between the REVERSE output and the R CUT output.

A high output is made to the tape counter during count up; a low output during count down.

Note: In the following descriptions, T REVERSE indicates the signal output made to the tape counter.

## 2-2-4. OPERATION DESCRIPTION

# 1. MODE SELECT SW

The MODE SELECT SW is used as the mechanism position detection SW in the stationary mode and as the mechanism control signal input during the transition mode of the mechanism operation. (See Table 2-2-2)

Note: The arrow indicates detection at the edge. For 0 1, detection is made at the leading edge. (0: LOW LEVEL, 1: HIGH LEVEL)

|            | MODE 1 | MODE 2 | MODE 3 |

|------------|--------|--------|--------|

| STOP MODE  | 0      | 1 → 0  | 0      |

| REC PAUSE  | 1 - 0  | 1 - 0  | 0      |

| REV        | 0      | 0      | 1 - 0  |

| PB/REC/CUE | 0 - 1  | 0      | 0 - 1  |

Table 2-2-2.

# 2. SOFTWARETIMER

#### 1) DURING LOADING

If the PB position is not detected within 5 seconds after commencing loading operations, the VCR automatically performs the unloading operations.

**DURING UNLOADING**If the STOP position is not detected within 6 seconds after commencing the unloading operations, the loading motor is stopped.

- 3) If STILL, REC/PAUSE, or PAUSE are continued for more than 5 minutes, the VCR automatically starts to unload.

- 4) If REV is continued for more than 5 minutes, the set is placed automatically in the PB mode.

#### 5) DURING FRONT LOADING

If the CDT SW low is not detected within 5 seconds after commencing front loading, the tape is automatically eiected.

#### 6) DURING EJECT

If the EED SW high is not detected within 5 seconds after commencing eject, the front loading motor is stopped.

# 3. Table 2-2-3 Shows Sensor Operations

| ESS   | EST | OPERATION                                             |

|-------|-----|-------------------------------------------------------|

| Н     | Н   | Key input cannot be accepted.                         |

| L → H | L-H | STOP mode is entered immediately.                     |

| L     | Н   | REW key input cannot be accepted.                     |

| L     | L H | STOP mode is entered immediately.                     |

| Н     | L   | REW is entered by key input other than STOP and EJECT |

| L → H | L   | AUTO REW is entered.                                  |

| L     | L   | Normal operaion                                       |

Table 2-2-3.

## 4. TIMER RECORDING

|     | POWER IN | SAFETY | STAGE | ESS | EST |

|-----|----------|--------|-------|-----|-----|

| (1) | Н        | Н      | L     | L   | L   |

| (2) | н        | Н      | L     | L   | Н   |

Table 2-2-4.

When the above conditions (1) or (2) are fulfilled, the set is placed in the REC mode when the TIMER REC input becomes high and the PWR OUT output becomes low.

When the TIMER REC input changes from high to low, the unload is stopped and the PWR OUT output becomes high. (See Table 2-2-4)

# 2-2-5. DESCRIPTION OF SPECIFIC OPERATIONS

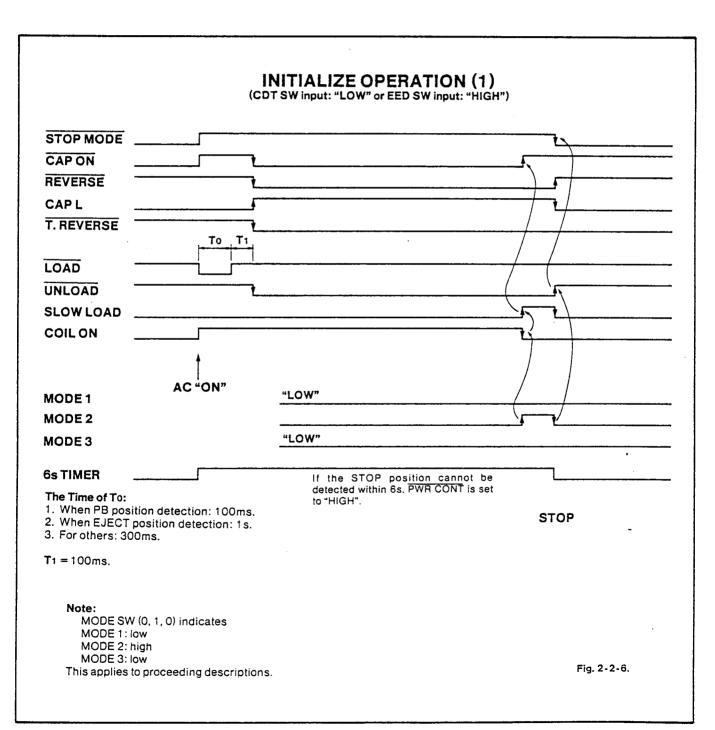

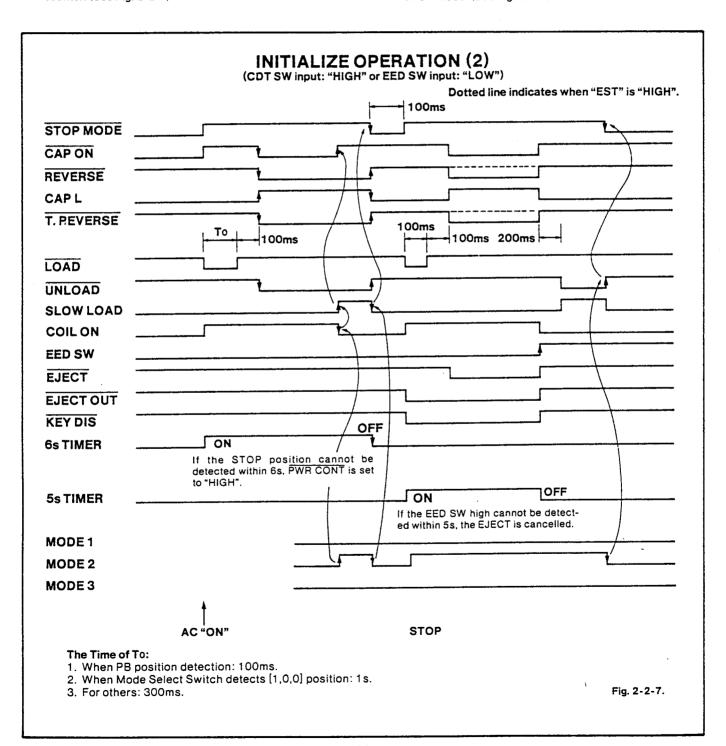

## 1) INITIALIZE (See Fig. 2-2-6)

- a) When the position data of the mode select switch are transmitted to the microcomputer, the loading motor runs in forward direction (CCW) for the following times: 100ms in PLAYBACK, 1s in EJECT (1, 0, 0) and 300ms in other modes. The latch coil is kept in the ON condition and the reel brake is released during this interval.

- After 100ms, the capstan motor is driven slowly in reverse (CCW), shifting into the unload operations.

T REVERSE is set to low and tape counter starts count down.

- c) When the MODE SELECT SW position [(0, 0, 0) (0, 1, 0)] is detected, the latch coil and capstan motor are switched OFF. In addition, the slow load is output, making the loading motor unload slowly. At this time, brakes are applied to both reels.

- d) When the MODE SELECT SW position [(0, 1, 0) (0, 0, 0)] is detected, the reverse (CW) loading motor is stopped, the STOP MODE becomes low and the VCR is placed in the STOP mode.

- e) When the CDT SW input is low or the EED SW is high, the initialize operation is completed. (Fig. 2-2-7)

- f) The EJECT OUT and KEY DIS outputs are made low. (See Fig. 2-2-7)

- g) The LATCH COIL is switched ON, the loading motor loads for 100ms, the reel brake is disengaged and held in this condition. (See Fig. 2-2-7)

- After 100ms, the capstan motor is driven slowly to take up tape slack. Count down command is sent to the tape counter. (See Fig. 2-2-7)

- i) The front loading motor is driven in the CW direction and the eject operation is performed. (See Fig. 2-2-7)

- j) When the EED SW input high is detected, the LATCH COIL and capstan motor are switched OFF. In addition, the SLOW LOAD and EJECT OUT outputs become high, making the loading motor unload slowly. At this time, brakes are applied to both reels. (See Fig. 2-2-7)

- k) When the MODE SELECT SW position [(0, 1, 0) (0, 0, 0)] is detected, the loading motor drive is stopped, the STOP MODE signal is set to low and the set is placed in the STOP mode. (See Fig. 2-2-7)

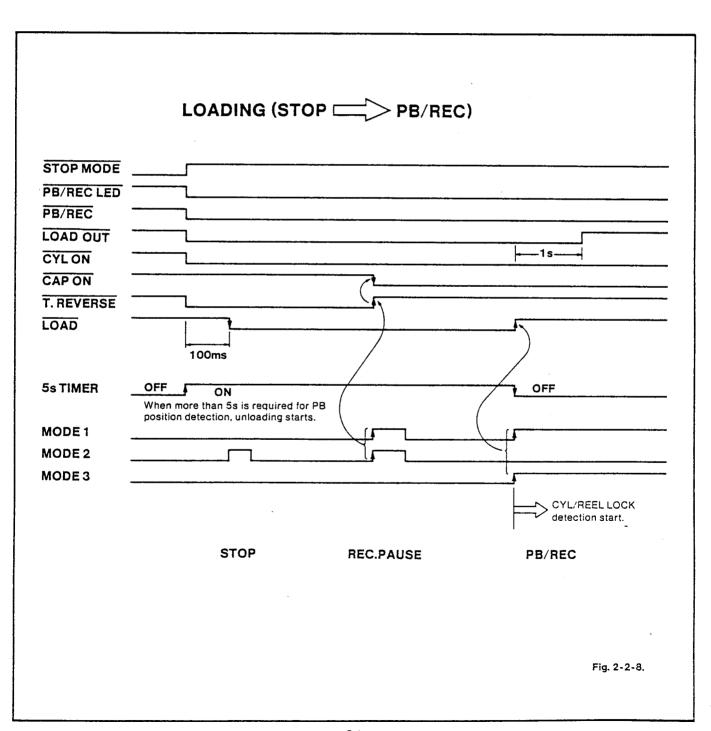

# 2) LOADING (STOP -- PB/REC) (See Fig. 2-2-8)

a) When the PB button alone or the PB and REC buttons are pressed simultaneously, the PB or PB and REC LEDs light up simultaneously.

At the same time:

- 1 CYL ON is set to low, starting the cylinder motor;

- 2 LOAD low, PB low or REC low outputs are sent to the servo circuit.

- 3 TREVERSE is set to low and output to the counter. After 100ms, the loading motor is driven in the forward direction (CCW) and the loading operations are performed.

- b) When the MODE SELECT SW position [(0, 0, 0) (0, 1, 0)] is detected, T REVERSE is set to high and the capstan motor is driven in the forward direction (CW).

- c) When the MODE SELECT SW position [(0, 0, 0) (0, 1, 0)] is detected, the loading motor is stopped and the CYL LOCK, and REEL LOCK checks are commenced.

- d) 1 second after c), the LOAD is set to high and the VCR is placed in the PB or REC stationary mode.

- e) When the PB or PB and REC buttons are pressed simultaneously and the MODE SELECT SW position (1, 0, 1) is not detected, the VCR is placed in the unload mode.

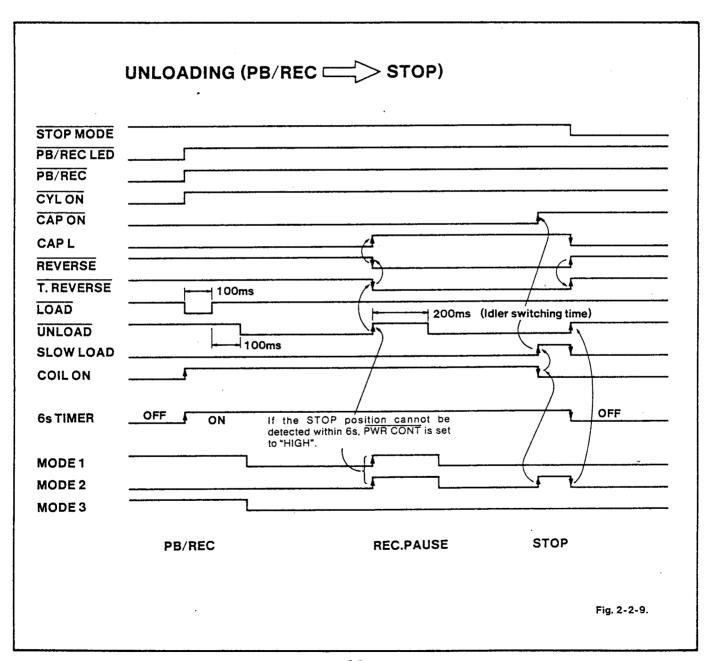

# 3) UNLOADING (PB/REC — STOP) (See Fig. 2-2-9)

When the STOP button is pressed during the PB (PB, CUE, REV, STILL) REC, or REC PAUSE mode the set is placed in the unload stop mode.

- a) PB or PB and REC LEDs go out.

At the same time, PB or REC is set to high, as well as CYL

ON, and the cylinder motor is stopped.

- b) The LATCH COIL is turned ON, loading (CCW) is performed for 100ms, the brake is disengaged and maintained in this condition.

- After 100ms, the loading motor is driven in the reverse direction (CW) and the unload operation is started.

- d) When the MODE SELECT SW position [(0, 0, 0) (1, 1, 0)] is detected, after a 200ms stop, the capstan motor is slowly driven in the reverse direction (CCW) to take up tape slack. T REVERSE is set to low.

- e) When the MODE SELECT SW position [(0, 0, 0) (0, 1, 0)] is detected, the capstan motor and the LATCH COIL are switched OFF and the loading motor is slowed down.

- f) When the MODE SELECT SW position [(0, 1, 0) (0, 0, 0)] is detected, the loading motor is stopped and the VCR is placed in the stop mode.

- g) When the STOP button is pressed and the set is placed in the unload operation, the 6-second timer operates immediately. If the MODE SELECT SW position (0, 1, 0) is not detected within 6 seconds, the loading motor is stopped.

In this condition all button inputs and function SW inputs are not accepted.

The set is initialized by turning AC power on.

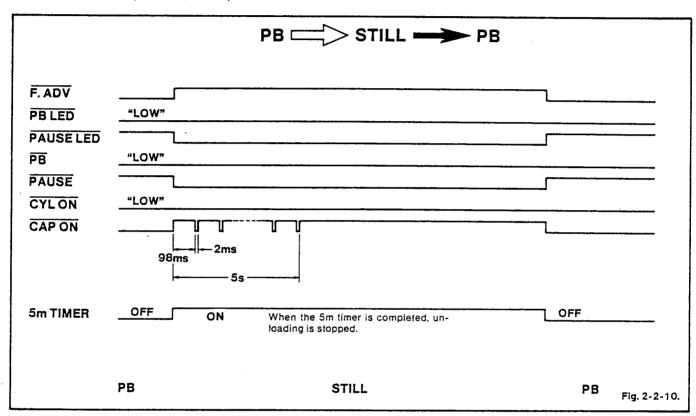

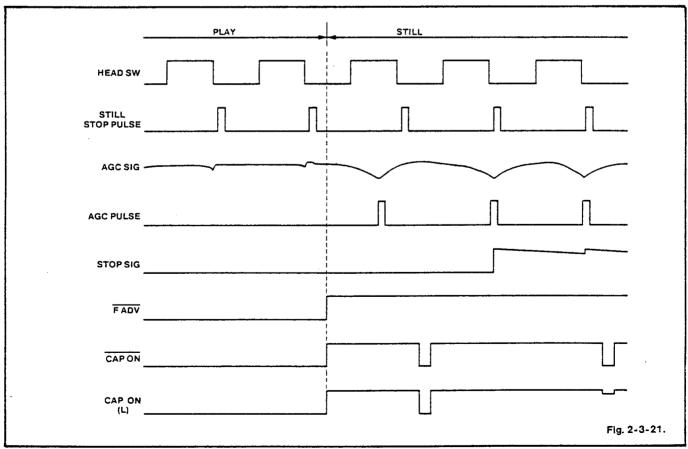

# 4) PB - STILL (See Fig. 2-2-10)

When the PAUSE button is pressed in the PLAYBACK mode. the capstan motor is stopped and the VCR is placed in the STILL mode.

- a) PAUSE low is output to the servo circuit, and the PAUSE LED lights up at the same time.

- b) A pulse of 98ms high and 2ms low is output for 1.5s to CAP ON for intermittent drive of the capstan motor.

- If the STILL mode is continued for more than 5 minutes. the set automatically unloads, and stops.

# 5) STILL → PB (See Fig. 2-2-10)

- When the PAUSE button is pressed in the STILL mode, PAUSE is set to high and the PAUSE LED goes out.

- At the same time, F ADV, CAP ON are set to low and the capstan motor is driven in the forward direction (CW).

6) PB  $\rightarrow$  CUE (See Fig. 2-2-11) When the FF button is pressed in the PLAYBACK mode, SEARCH is set to low; the cylinder and the capstan motors run at high speed.

7) CUE — PB (See Fig. 2-2-11)

When the PB button is pressed in the CUE mode, SEARCH is set to high, and the VCR shifts to the PB mode.

|                                |             | PB CUE PB |    |              |

|--------------------------------|-------------|-----------|----|--------------|

| PB LED PB CYL ON CAP ON SEARCH | "LOW" "LOW" |           |    |              |

|                                | PB          | CUE       | PB | Fig. 2-2-11. |

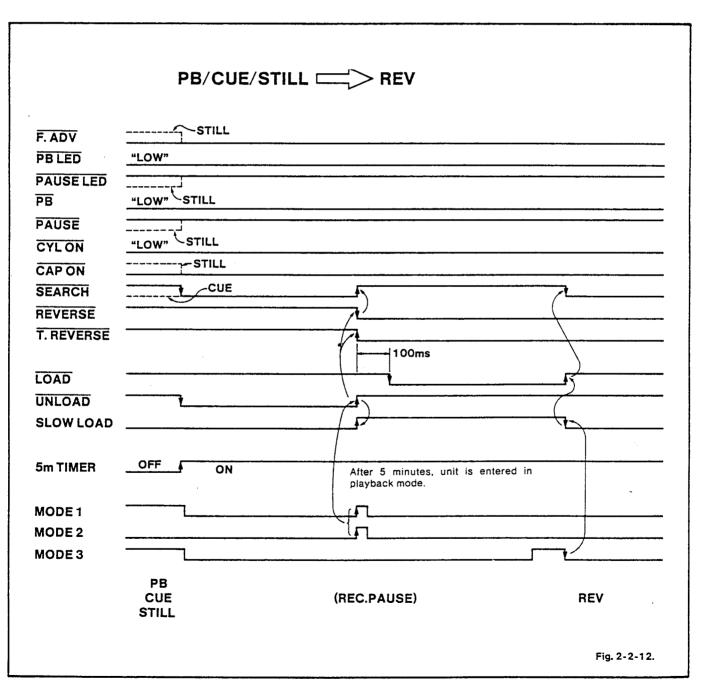

# 8) PB/CUE/STILL → REV (See Fig. 2-2-12)

When the REW button is pressed in either the PB CUE, or STILL modes the VCR is placed in the high-speed reverse playback mode after the following steps:

- a) SEARCH is set to low and the capstan is driven quickly in the forward direction (CW). During this interval, STILL and CAP ON are set to low simultaneously, to maintain tape tension.

- b) The loading motor is driven in the reverse direction (CW) and the pinch roller is separated from the capstan.

- c) When the MODE SELECT SW position (1, 1, 0) is detected, the capstan motor is driven in the reverse direction (CCW) at normal speed and switches the idler to the supply reel side. The loading motor forward drive (CW) is stopped. T REVERSE is set to low and the counter starts count down.

- After 100ms, the loading motor is driven in the forward direction (CCW) at low speed.

- e) When the MODE SELECT SW position [(0, 0, 1) (0, 0, 0)] is detected, the loading motor is stopped, SEARCH is set to low, the capstan motor is driven quickly in the reverse direction (CCW), the cylinder motor is driven at high speed; the VCR is placed in the REV stationary mode.

- f) When the REV mode is kept continuously for more than 5 minutes, the VCR automatically reverts to the PB mode.

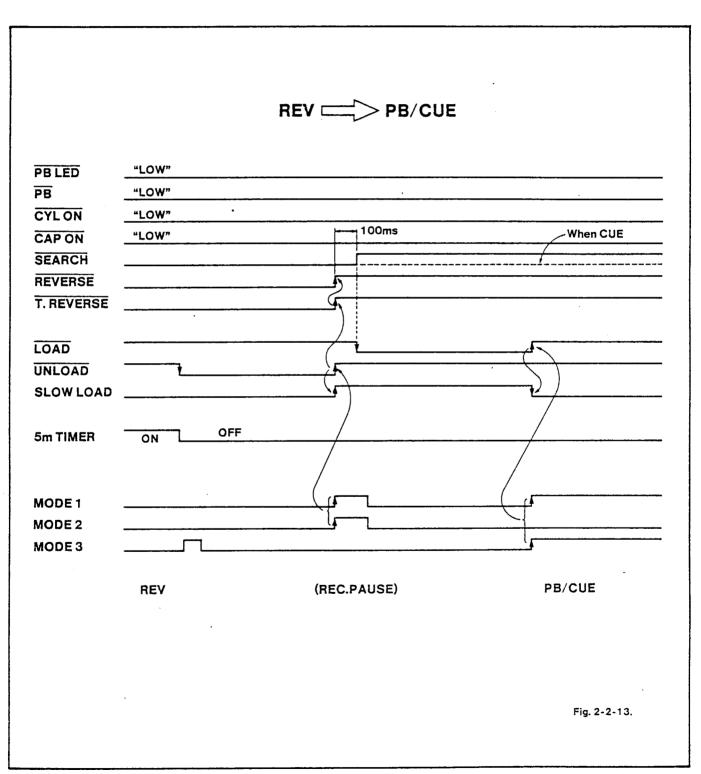

# 9) REV - PB/CUE (See Fig. 2-2-13)

When the PB button is pressed in the REV mode, the set shifts to the PB mode.

- a) Until the MODE SELECT SW position (1, 1, 0) is detected, the loading motor is driven in the CW (unload) direction.

- b) When the MODE SELECT SW position is detected, the capstan motor is driven in the forward direction (CW) and the idler is switched to the take up reel side. T REVERSE is set to high and the counter starts count up.

- c) After 100ms, the capstan speed is driven at the normal speed (when shifting into CUE, SEARCH is kept low) and low speed loading (CCW) is performed.

- d) When the MODE SELECT SW position (1, 0, 1) is detected, the loading motor is stopped and the VCR shifts into the PB or CUE stationary mode.

10) STILL  $\rightarrow$  CUE (See Fig. 2-2-14) When the FF button is pressed in the STILL mode, the VCR shifts into the CUE mode.

- a) PAUSE high is output to the servo circuit.

- b) SEARCH and CAP ON are set to low and the capstan motor is driven in the forward direction (CCW) quickly.

|                                             | STILL CUE   |              |

|---------------------------------------------|-------------|--------------|

| F. ADV PB LED PB PAUSE CYL ON CAP ON SEARCH | "LOW" "LOW" |              |

| 5s TIMER                                    | ON COFF     |              |

|                                             |             | Fig. 2-2-14. |

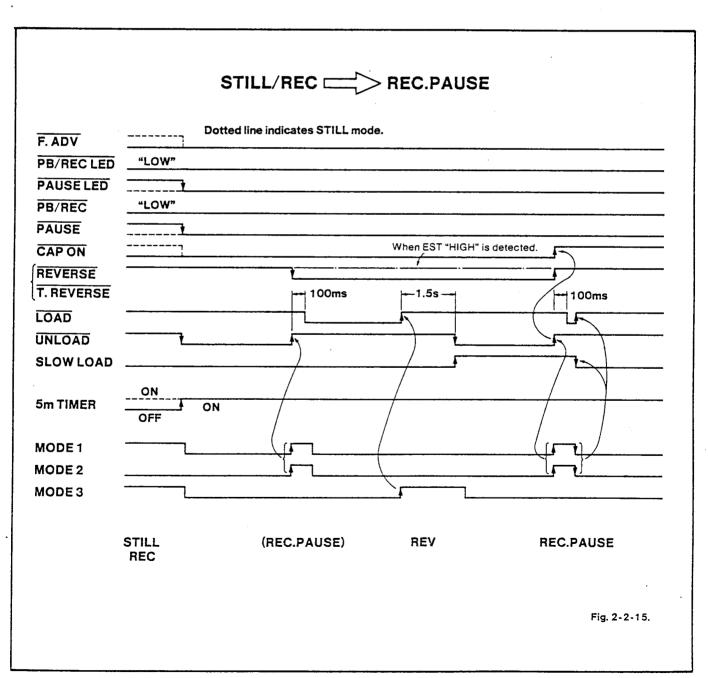

### 11) STILL/REC - REC PAUSE (See Fig. 2-2-15)

When the PAUSE button is pressed in the REC mode, the set shifts into the REC PAUSE mode.

- The PAUSE LED lights up and PAUSE is set to low. (When shifting from STILL, F. ADV is low.)

- The loading motor unloads (CW) until the MODE SELECT SW position (1, 1, 0) is detected.

- c) The capstan motor is driven in the reverse direction (CCW) and the idler is switched to the supply reel side. T REVERSE is set to low.

- After 100ms, the loading motor is driven in the forward direction (CCW) and the load operation is performed.

- e) When the MODE SELECT SW position (0, 0, 1) is detected, the loading motor is stopped. At this time, it is in the REV position.

- f) The tape is rewound in the reverse direction by the pinch roller for 1.5 seconds.

- g) After 1.5 seconds, the loading motor unloads slowly (CW) until the MODE SELECT SW position (1, 1, 0) is detected.

- h) Running of the capstan motor in the reverse direction (CCW) is stopped. TREVERSE is set to high.

- After 100ms, the loading motor loads slowly (CCW) until the MODE SELECT SW position [(1, 1, 0) - (0, 0, 0)] is detected, and the VCR is placed in the REC PAUSE stationary mode.

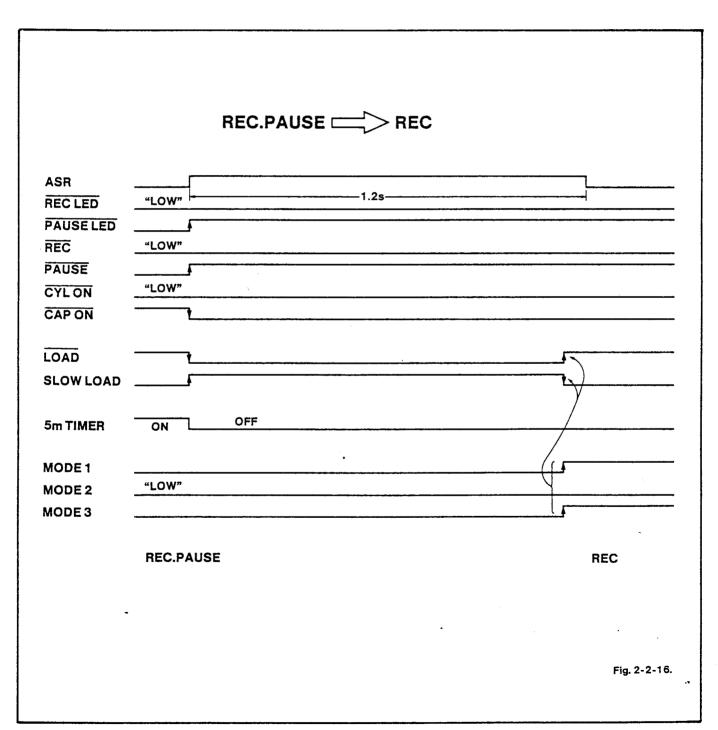

### 12) REC PAUSE - REC (See Fig. 2-2-16)

When the PAUSE button is pressed in the REC PAUSE mode, the set is returned to the REC mode.

- a) The PAUSE LED is switched OFF and PAUSE is set to high. The ASR is set to high for 1.2s and the assemble record signal is output.

- The capstan motor is driven in the forward direction (CW).

- c) The loading motor loads slowly (CCW).

- d) When the MODE SELECT SW position (1, 0, 1) is detected, the loading motor is stopped and the VCR is placed in the REC mode.

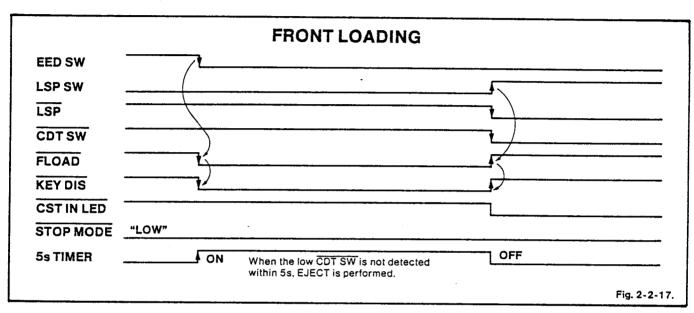

### 13) FRONT LOAD (See Fig. 2-2-17)

When the cassette is inserted:

- a) The EED SW input changes from high to low.

- b) The KEY DIS, F LOAD outputs are set to low, the front loading motor is driven in the CCW direction and the cassette holder is lowered.

- c) When the cassette holder is lowered and the LSP SW input is set to high, the front loading motor drive is stopped and the LSP output is set to low.

- d) When the CDT SW input becomes low, the TAPE IN LED lights up.

- e) If the low CST SW input is not detected within 5 seconds, the cassette is automatically ejected.

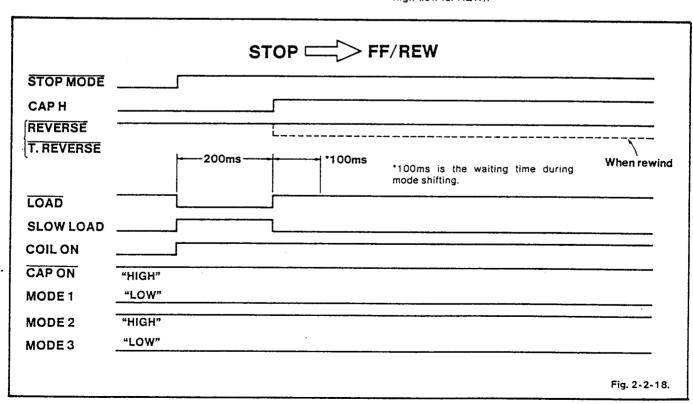

### 14) STOP → FF/REW (See Fig. 2-2-18)

- a) When the FF (REW) button is pressed, the latch coil is switched ON, the loading motor loads (CCW) slowly for 200ms and the reel brake is disengaged and maintained in this condition.

- b) CAP H is set to high and the capstan motor is driven in the forward direction (CW) [reverse (CCW) for REW] at maximum speed. At the same time, T REVERSE is set to high (low for REW).

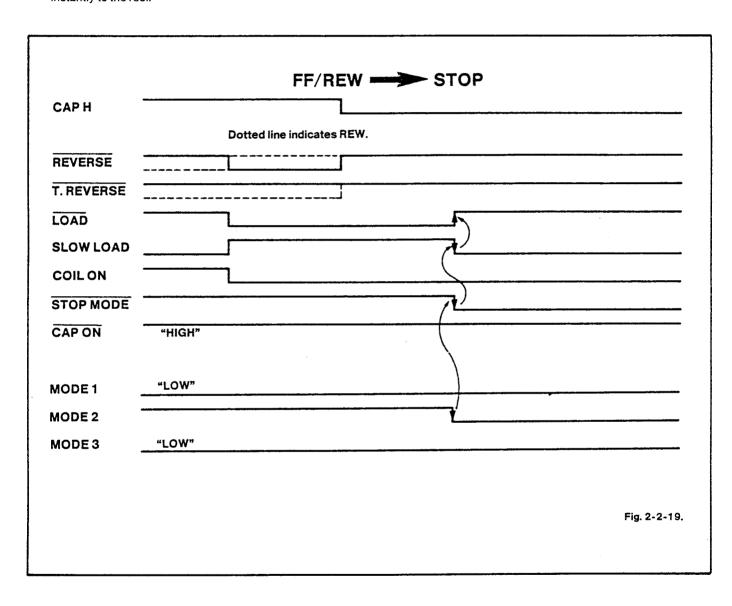

15) FF/REW — STOP (See Fig. 2-2-19) When the STOP button is pressed in the FF/REW mode.

- A reverse (CCW) signal is sent to the capstan motor [forward (CW) for REW] for 100ms and the brake is applied to the capstan motor.

- b) CAP H is set to low and the capstan motor drive is stopped.

- The latch coil is turned off; the loading motor unloads (CW) until the MODE SELECT SW position [(0, 1, 0) (0, 0, 0)] is detected. With this operation, the brake is applied instantly to the reel.

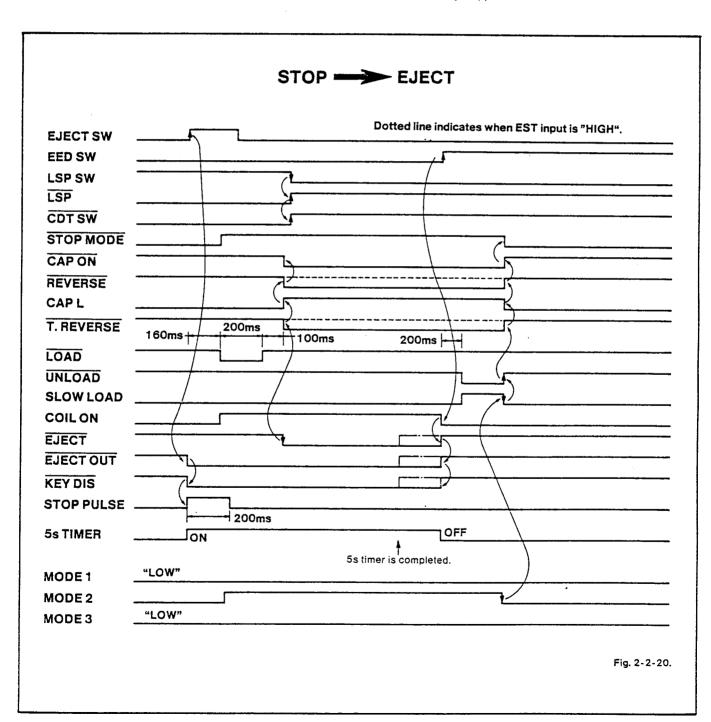

### 16) STOP → EJECT (See Fig. 2-2-20)

When the EJECT button is accepted:

- a) A STOP PULSE (200ms, high) is output and the EJECT OUT low output and the KEY DIS output are set to low. (If the set was not in the STOP mode, this operation places the set in the STOP mode.)

- b) If the STOP MODE signal is low, the latch coil is turned ON, the loading motor loads for 200ms and the reel brake is disengaged and maintained in this condition.

- After 100ms, the capstan motor is driven slowly and tape slack is removed.

- d) The front loading motor is driven in the CW direction and the tape is ejected.

- e) When the cassette holder rises and the high EED SW input is detected, the latch coil is turned OFF. In addition, the SLOW LOAD, EJECT OUT outputs are set to high and the loading motor unloads slowly. At this time, brakes are applied to both reels.

- f) When the MODE SELECT SW position [(0, 1, 0) (0, 0, 0)] is detected, the capstan and loading motor drives are stopped, the STOP MODE output is set to low and the set is placed in the STOP mode.

Note: For operation e), if the high EED SW input is not detected within 5 seconds, the front loading motor is automatically stopped.

### 17) CHANGING TO THE NEXT MODE VIA THE STOP MODE

In the following cases, entry into the new mode is always executed via the STOP mode.

- a) During PB/STILL/CUE/REVIEW, when the EJECT button is pressed.

- b) During FF/REW, when the EJECT button is pressed.

- During FF/REW when the PB button is pressed, or when the PB and REC buttons are pressed simultaneously.

- d) During FF, when the REW button is pressed.

- e) During REW, when the FF button is pressed.

18) During loading, when the FF/REW/EJECT button is pressed, the set moves into the next operation after completing loading.

Note: For items 17, 18, see the Mode Shift Chart.

|                |              |              |              |                 |            |             | ·             |

|----------------|--------------|--------------|--------------|-----------------|------------|-------------|---------------|

| INPUT KEY MODE | STOP         | PLAY         | REC          | PAUSE           | FF         | REW         | EJECT         |

| STOP           | STOP         | PLAY         | REC          | STOP<br>PAUSE   | FF         | REW         | EJECT         |

| PLAY           | STOP         |              | REC          | STILL           | CUE        | REV         | STOP<br>EJECT |

| REC            | STOP         |              |              | REC<br>PAUSE    |            |             | ,             |

| STILL          | STOP         |              | REC<br>PAUSE | PLAY            | CUE        | REV         | STOP<br>EJECT |

| REC PAUSE      | STOP         |              |              | REC             |            |             |               |

| STOP PAUSE     | STOP         | STILL        | REC<br>PAUSE | STOP            | FF         | REW         | EJECT         |

| CUE            | STOP         | PLAY         |              |                 |            | REV         | EJECT         |

| REV            | STOP         | PLAY         |              |                 | CUE        |             | EJECT         |

| FF             | STOP         | PLAY         | REC          |                 |            | REW         | EJECT         |

| REW            | STOP         | PLAY         | REC          |                 | FF         |             | EJECT         |

| LOADING        | LOAD<br>STOP | PLAY         | REC          | Accept-<br>able | LOAD<br>FF | LOAD<br>REW | LOAD<br>EJECT |

| UNLOADING      | STOP         | STOP<br>PLAY | STOP<br>REC  | STOP<br>PAUSE   | STOP<br>FF | STOP<br>REW | STOP<br>EJECT |

Note:

LOAD STOP means shifting to STOP mode after loading. STOP PLAY means shifting to STOP mode and then entry into PLAY mode. Table 2-2-5.

# 2-2-6. OUTPUT SIGNALS IN STEADY STATE

Table 2-2-6 shows output signals in steady state.

| MODE        | STOP | PLAY | REC | STOP<br>PAUSE | STILL | REC<br>PAUSE | CUE | REV | FF | REW | TIMER | FLOAD | EJECT | LOADING | UN-<br>LOADING | DEW          |

|-------------|------|------|-----|---------------|-------|--------------|-----|-----|----|-----|-------|-------|-------|---------|----------------|--------------|

| PLAY OUT    |      | 0    |     |               | 0     |              | 0   | 0   |    |     |       |       |       | V       |                |              |

| REC OUT     |      |      | 0   |               |       | 0            |     |     |    |     | 0     |       |       | ٥       |                |              |